線幅サブミクロンも視野に パッケージ向け露光装置でウシオとAppliedが協業:大型化と微細配線の要求に応える(1/2 ページ)

ウシオ電機とApplied Materialsは2023年12月、戦略的パートナーシップの締結を発表した。両社が「DLT(Digital Lithography Technology)」と呼ぶ、半導体パッケージ基板向けの新しいダイレクト露光装置を早期に市場に投入し、大型化や配線の微細化など半導体パッケージ基板への要求に応えることを目指す。

ウシオ電機とApplied Materials(以下、Applied)は2023年12月、戦略的パートナーシップの締結を発表した。先端の半導体パッケージ基板で要求が高まる基板配線の微細化を実現すべく、新しいダイレクト露光装置「DLT(Digital Lithography Technology)」の早期市場投入を目指す。

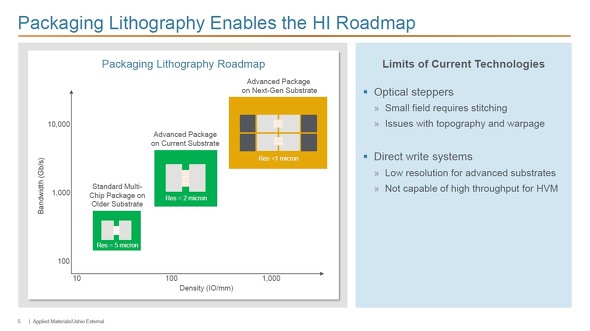

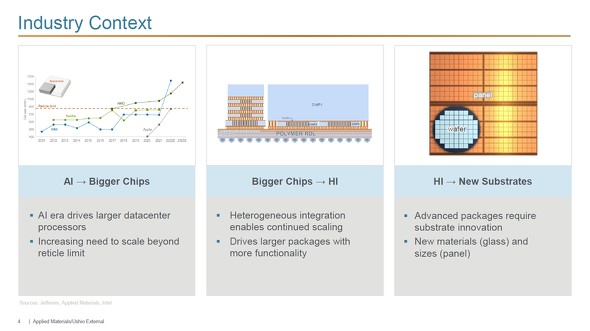

半導体製造プロセスの微細化が困難かつ高コストになる中、機能が異なる複数のチップを1パッケージに統合/積層するヘテロジニアスインテグレーション(HI:Heterogenious Integration)によって、半導体の高性能化、高機能化を進める動きが活発になっている。HIでより多くのチップを統合するために、より微細な配線や優れた電気特性を実現した大型パッケージ基板が求められるようになっている。

チップレット集積のような、機能が異なる複数のチップを1パッケージに統合するヘテロジニアスインテグレーション(HI:Heterogenious Integration)では、大型のパッケージ基板や、ガラスのような新しい材料を用いたパッケージ基板が求められるようになっている[クリックで拡大] 出所:Applied Materials/ウシオ電機

チップレット集積のような、機能が異なる複数のチップを1パッケージに統合するヘテロジニアスインテグレーション(HI:Heterogenious Integration)では、大型のパッケージ基板や、ガラスのような新しい材料を用いたパッケージ基板が求められるようになっている[クリックで拡大] 出所:Applied Materials/ウシオ電機サブミクロンの線幅まで視野に入れた「DLT」

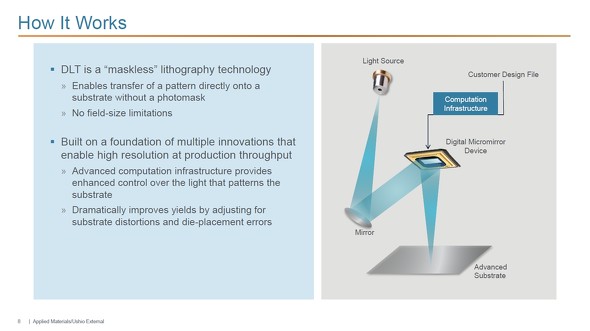

ウシオ電機とAppliedが早期投入を目指すDLTは、こうした先進パッケージ基板の要求に応えるためのダイレクト露光装置だ。通常の露光装置は、金属の配線パターンを焼き付けたガラスマスク(フォトマスク)を使用してパターニングを行う。一方、ダイレクト露光装置は、CADで設計したパターンデータを、ガラスマスクを使わず基板に直接転写する。マスクを作る必要がないので低コストなことに加え、CADデータを変えるだけでパターンを変更できるという利点もある。

DLTでは、光源から出力されたレーザーをミラーに当てて反射させ、DMD(Digital Micromirror Device/アレイ上に小さなミラーが敷き詰められているデバイス)をコンピュータで制御して回路パターンを描画する。DMDのミラー1個1個の角度をコンピュータで精密に制御することで、微細な基板配線の描画が可能になる。「DLTの“Digital”は、CADの“デジタル”データを用いるダイレクト露光や、DMDの精密な“デジタル”制御を指している」(アプライド マテリアルズ ジャパン)

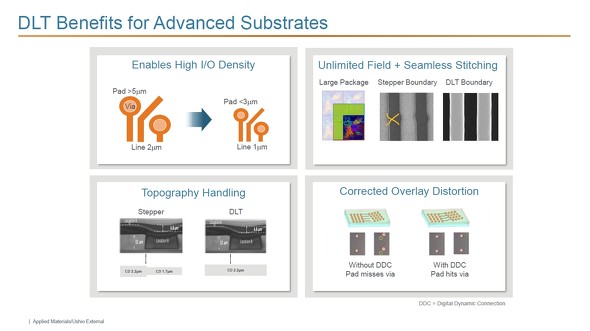

DLTの特徴は、1μmのL/S(ライン/スペース)や3μmのパッドサイズといった、微細な基板配線をパターニングできるようになることだ。

DLTのロードマップでは、L/Sが2μmから1μm、サブミクロンまで視野に入っている。「(多層配線の)先進パッケージ基板では、特にロジックに接続する上部基板の配線幅が非常に狭くなっている。半導体業界全体で2μmや1μmのL/Sを目指す中、それほど微細な配線を正確に描画できる露光装置はまだ存在していない。ウシオ電機とAppliedの協業により、そうした装置(DLT)を提供できるようになる」(アプライド マテリアルズ ジャパン)

DLTは、位置合わせを補正する機能も備えている。樹脂やガラスでできているパッケージ基板は、反りやうねりが大きくなる傾向がある。従来のガラスマスクでは、こうしたうねりにより露光のフォーカスがずれてしまうことがある。DLTは、デジタル制御によって、こうしたずれを調整し、正しい位置にパターニングすることが可能だ。

大型パッケージ基板のパターニングでも優位性を発揮する。大面積のパッケージ基板を露光する場合、複数のガラスマスクを作成し、それらをつないで露光するスティッチングが用いられる。ただ、スティッチングでは、マスク同士のつなぎ目でずれが生じることが課題になっている。「L/Sが2μm/2μmレベルになってくると、スティッチング時のずれを許容できなくなってくる」(アプライド マテリアルズ ジャパン)。これに対し、DLTは「“座標”を指定して描画する」イメージなので、微細な基板配線でもずれがほとんど生じない。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- 次世代パワー半導体 「期待の5材料」の現在地