東北大ら、「近未来版」の確率論的コンピュータを開発:半導体回路+スピントロニクス素子で(1/2 ページ)

東北大学と米国カリフォルニア大学サンタバーバラ校らの研究チームは、確率的なアルゴリズムを効率よく実行でき、製造も比較的容易な「近未来版の確率論的コンピュータ」を開発、その動作を検証した。「最終形態の確率論的コンピュータ」では、現行の半導体コンピュータに比べ、面積を約4桁、エネルギー消費を3桁、それぞれ削減できることを確認した。

将来的には面積で約4桁、エネルギー消費で3桁を削減可能

東北大学電気通信研究所の小林奎斗大学院生(研究当時)や金井駿准教授、大野英男教授、深見俊輔教授らと、米国カリフォルニア大学サンタバーバラ校のKerem Camsari博士らによる研究チームは2024年4月、確率的なアルゴリズムを効率よく実行でき、製造も比較的容易な「近未来版の確率論的コンピュータ」を開発、その動作を検証したと発表した。「最終形態の確率論的コンピュータ」では、現行の半導体コンピュータに比べ、面積を約4桁、エネルギー消費を3桁、それぞれ削減できることを確認した。

東北大学および米国カリフォルニア大学サンタバーバラ校と、米国パデュー大学の共同研究チームはこれまで、スピントロニクス確率論的コンピュータのデモシステムを開発し、組み合わせ最適化や機械学習、量子多体計算、ベイズ推定などの原理実証を行ってきた。これとは別に東北大学は、確率動作スピントロニクス素子の性能向上に向けた研究に取り組んできた。こうした中、比較的容易かつ低コストで製造が行え、高い計算性能とエネルギー効率を実現するハードウェアの開発が求められていた。

そこで今回、半導体回路とスピントロニクス素子を融合した近未来版確率論的コンピュータを開発し、その動作を検証した。また、プロセス設計キットを用い、スピン素子を主体とした確率論的コンピュータの最終形態で実現される性能を確認した。

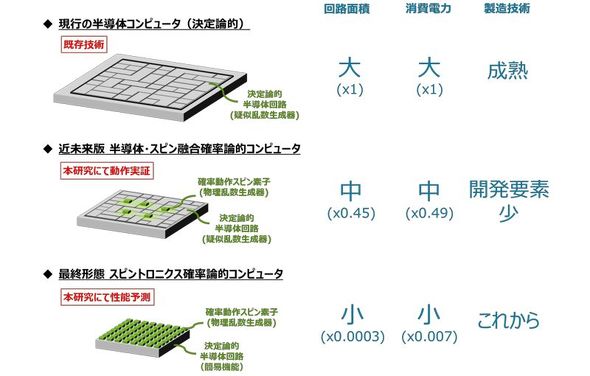

実験では、「現行の半導体コンピュータ」、今回開発した「近未来版の半導体・スピン融合確率論的コンピュータ」および、スピン素子を主体とした「最終形態の確率論的コンピュータ」について検証した。

現行の半導体コンピュータでは、確率的アルゴリズムを実行する場合に疑似乱数生成器を用いる。これだと、回路面積と消費するエネルギーが大きくなる。最終形態の確率論的コンピュータは、確率的に振る舞う多数のスピン素子が必要で、これを実現するためには開発すべき技術が残されているという。これに対し、開発した近未来版の確率論的コンピュータは、従来型の疑似乱数生成器を内蔵した半導体回路と、わずかな確率動作スピン素子で構成される。このため、製造は比較的容易だという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ