EE Times Japan >

先端技術 >

東北大ら、「近未来版」の確率論的コンピュータを開発:半導体回路+スピントロニクス素子で(2/2 ページ)

» 2024年04月12日 13時30分 公開

[馬本隆綱,EE Times Japan]

プロトタイプを作製して評価

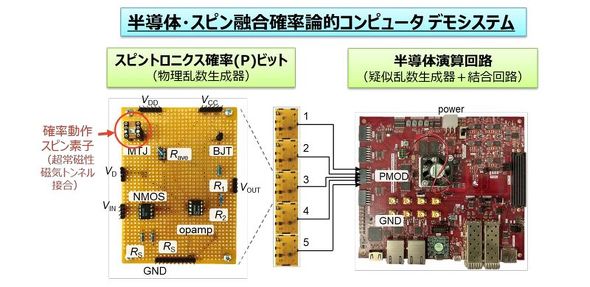

研究チームは、半導体・スピン融合確率論的コンピュータのプロトタイプを作製し、確率的サンプリングによる推定と深層ボルツマン機械学習の性能評価を行った。このシステムは、確率動作スピン素子からなる5つのスピントロニクス確率ビット(Pビット)が生成する物理乱数で、FPGA内にある大量の疑似乱数生成器を駆動して演算が行われるよう設計されている。

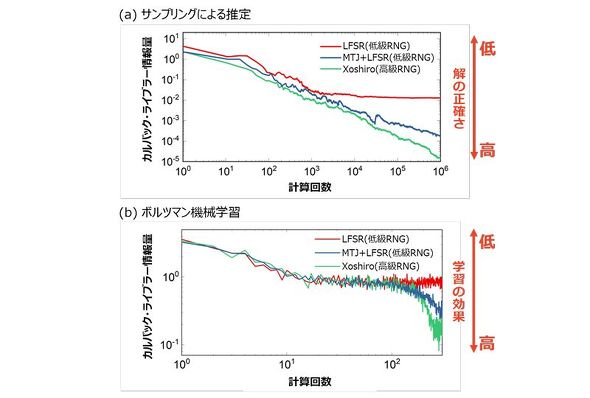

実験では、線形帰還シフトレジスタ(LFSR)および、LFSRが出力するビット列に数学的な処理を施し、そのランダム性を高めた疑似乱数生成器(Xoshiro)と、LFSRを確率動作スピン素子で駆動した場合(MTJ+LFSR)の効果を比較した。

この結果、確率動作スピン素子でLFSRを駆動した場合でも、高級なXoshiroと同じように、計算を重ねることで解の精度や学習の効果が高まることを確認。高い計算性能を少ないリソースで実現できることが分かった。

さらに、プロセス設計キットを用い、LFSRとXoshiro、スピン素子からなるPビットを形成するために必要なトランジスタ数と、1つの乱数を生成するのに必要なエネルギーを比べた。そうしたところ、最終形態のスピントロニクスPビットはXoshiro Pビットに比べて、トランジスタ数は0.0003倍、消費エネルギーは0.007倍で済むことが分かった。

関連記事

廃棄される「ズワイガニ」が半導体材料に、東北大学らが発見

廃棄される「ズワイガニ」が半導体材料に、東北大学らが発見

東北大学は2024年3月25日、カニ殻から得られるキトサンのナノファイバーシートが、直流/交流変換、スイッチング効果、整流作用などの半導体特性と蓄電効果を発現することを発見したと発表した。 磁気記録媒体を3次元化、HDDの容量拡大が可能に

磁気記録媒体を3次元化、HDDの容量拡大が可能に

物質・材料研究機構(NIMS)と米国Seagate Technology、東北大学の研究グループは、磁気記録媒体を3次元化すれば、ハードディスクドライブ(HDD)で多値記録ができることを実証した。10Tビット/in2を超える高密度磁気記録が可能となる。 低温でも充放電が可能に マグネシウム蓄電池向けの新たな正極材料

低温でも充放電が可能に マグネシウム蓄電池向けの新たな正極材料

東北大学は、マグネシウム蓄電池(RMB)に向けて、岩塩型構造の新たな正極材料を開発した。90℃という低温でマグネシウム(Mg)の挿入や脱離ができることを実証した。 磁気メモリの高集積化を可能にする技術 東北大らが開発

磁気メモリの高集積化を可能にする技術 東北大らが開発

東北大学と東邦大学の共同研究グループは、らせん磁性体のねじり方向「キラリティー」を室温で制御/検出できる、「マンガン金合金(MnAu2)薄膜」を開発した。ビット間干渉がなく高集積かつ堅固な磁気メモリを実現することが可能となる。 次世代メモリ材料における水素の拡散運動を解明

次世代メモリ材料における水素の拡散運動を解明

東北大学らの研究グループは、素粒子「ミュオン」を用いて、二酸化バナジウム(VO2)における水素の拡散運動を解明したと発表した。研究成果は高密度の抵抗変化型メモリ(ReRAM)開発につながる可能性が高いとみられる。 トポロジカル磁気構造を「作り分け」 超低消費電力デバイスの実現へ

トポロジカル磁気構造を「作り分け」 超低消費電力デバイスの実現へ

東北大学と独マインツ大学による共同研究チームは、人工反強磁性体を用いて、「メロン」や「アンチメロン」「バイメロン」と呼ばれるトポロジカル磁気構造を作り分けることに成功した。反強磁性トポロジカル磁気構造を用い、電力消費が極めて少ないデバイスを実現することが可能となる。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

Special SitePR

あなたにおすすめの記事PR