チップレット設計期間をどう短縮するのか 米新興が提案:モジュール式プラットフォーム(1/2 ページ)

チップレットへの注目度が高まるにつれて、チップレット設計における課題も出てきた。米国のスタートアップBaya Systemsは、そうした課題に応えるソリューションを明らかにした。

チップレット技術を手掛ける米国のスタートアップBaya Systems(以下、Baya)はステルスモードから脱し、チップレットに関する技術の詳細を明らかにした。

BayaのCCO(最高商務責任者)を務めるNandan Nayampally氏は、米国EE Timesとのブリーフィングで、「SoC(System on Chip)とチップレットのシステム設計、ソフトウェア開発の複雑さが爆発的に増大する中、チップレットの分析、設計、展開を加速する必要性も高まっている」と語った。

同氏は、「Bayaのより広範な課題は、われわれが現在“インテリジェントコンピューティング”と呼んでいるヘテロジニアスコンピューティング環境において、AI(人工知能)ワークロードが直面するデータ移動のボトルネックに取り組むことだ」と述べた。

Nayampally氏によると、より複雑なメモリ階層と処理ソリューションが結合されるとしても、データ移動を削減するには、より統合的なシステムが必要だという。同氏は、「チップレットは解決策を提供するが、標準化されていても、チップレットとSoC両方のソフトウェア開発が複雑になるため、エンドツーエンドのワークフローをサポートするツールが必要になる」と付け加えた。

Nayampally氏は、「チップレットの利点を十分に活用するには、特にシステムの大型化に伴って多くの課題が生じる。性能を保証できることが必須だが、これらの異なる処理要素間で、それをどのように行うのかが問題だ」と述べる。

同氏は、「市場投入までの時間は短縮されているにもかかわらず、コストと消費電力も考慮しなければならない。Bayaは、マルチチップまたはマルチクラスタシステムと、より複雑なさまざまな処理要素を組み合わせた展開において、分析と設計、開発を加速させるアプローチをとっている」と述べている。

チップレット設計を加速するプラットフォーム

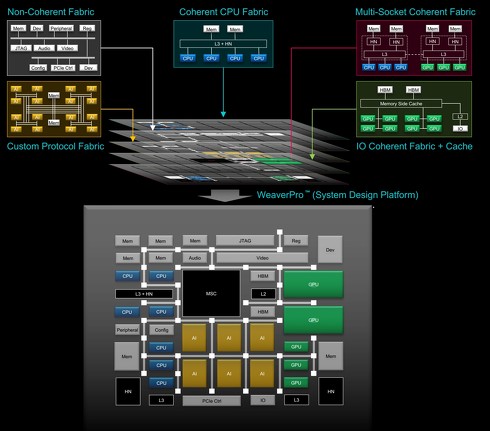

Nayampally氏によると、同社のアルゴリズム駆動型システムアーキテクチャプラットフォーム「WeaverPro」とスケーラブルなIP(Intellectual Property)およびキャッシュファブリックである「Weave IP」と組み合わせることで、データ駆動型の設計と最適化を通じてチップレットアーキテクチャを構築するための全てのステップをまとめることができるという。「ファブリックは多層構造で設計されており、実際にプロトコルに依存しないトランスポートが可能で、その上にプロトコルが効率的に積み重ねられている」と同氏は説明している。

Nayampally氏によると、全てを並列化するのではなく、必要に応じて一般的なワイヤや特殊な専用ワイヤを使用することで、コスト、ロジック、電力に対処できるという。

BayaのWeaverPro基本ソフトウェアプラットフォームには、効率的なメモリおよびキャッシュアーキテクチャの迅速な設計、フリーフォームキャッシュおよびメモリ階層の解析、ワークロードシミュレーションおよびグローバルシステムアーキテクチャの最適化、チップレットパーティションをサポートする「Cache Studio」が含まれる。

一方、「Fabric Studio」は、データ駆動型の最適なオンダイファブリックマイクロアーキテクチャの設計、設計パラメータと性能の静的解析と最適化、物理特性を考慮した設計の生成に使用できる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- Intelがアイルランド工場を完全子会社化、Apolloから49%買い戻し

- 次世代パワー半導体向け接合材を開発、エレファンテック