アナログICを薄膜化して3次元積層、レガシープロセスで:日清紡マイクロデバイスとOKIが共同開発(2/3 ページ)

局所的なシールドでクロストークの問題も解決

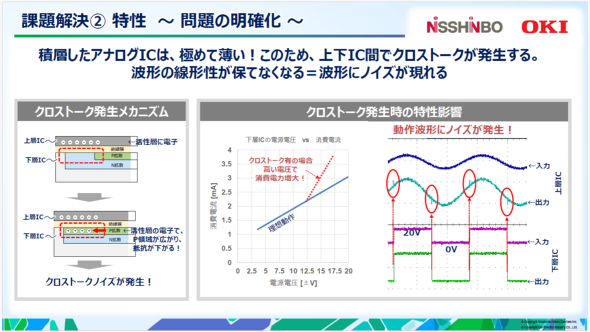

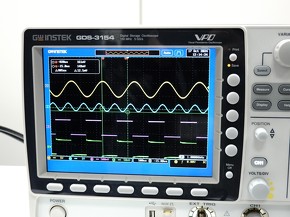

薄膜アナログICの厚みは約5μmと極めて薄い。そのため、上下のアナログICが近接し、クロストークノイズが発生してしまう。クロストークがあると、高い電源電圧において消費電力が高くなる他、動作波形にノイズが発生する。

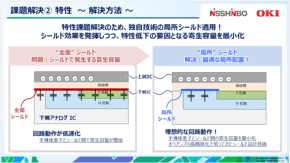

日清紡マイクロデバイスは、独自の「局所シールド」技術を適用することで、このクロストークを抑えた。アルミのシールド膜を形成し、それを上層アナログICと下層アナログICの間に挟むことで静電誘導を抑え、クロストークの発生を防ぐ。ただし、全面的にシールドを施すと、今度は半導体素子とシールド間で寄生容量が増加するという問題が起こる。寄生容量を充電しないと次の動作に移れないので、回路動作が遅くなってしまう。

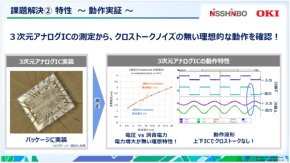

そこで、全面ではなく局所的にシールドを形成することで、寄生容量を最小限に抑えつつ、クロストークの発生も抑えることに成功した。ワイヤボンディングで積層したアナログICを動作させたところ、「電力増大のない理想的な特性を得られた」(日清紡マイクロデバイス)とする。ノイズの発生もなかった。

日清紡マイクロデバイスAT 生産技術部 専門課長 工学博士である緒方敏洋氏は、「どこに局所シールドを適用するかは、これまで当社がオペアンプの高精度化技術で培ってきたノウハウを生かしている。詳細は明かせないが、一定のルールはある」と語った。

レガシープロセスで再配線が可能

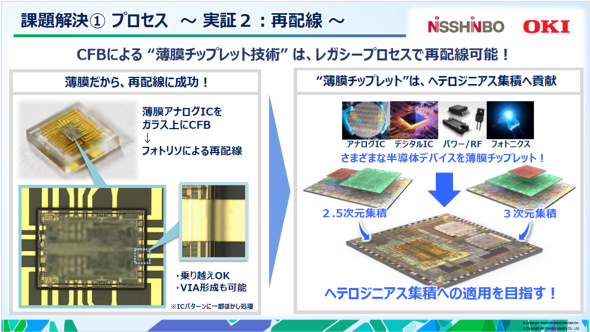

薄膜アナログICは極めて薄いので、一般的な半導体リソグラフィによる再配線の加工が可能になる。TSV(シリコン貫通ビア)による3次元集積のように最先端の高額な装置を使わず、レガシーのプロセスを適用できることが大きなメリットだ。

今回、OKIは薄膜化したアナログICをガラス基板上にCFBで接合し、フォトリソグラフィによる再配線に成功した。OKIは、CFBプロセスと再配線プロセスを組み合わせた技術を「薄膜チップレット技術」とし、さまざまな半導体デバイスを集積するヘテロジニアス集積への適用を目指すと意気込む。

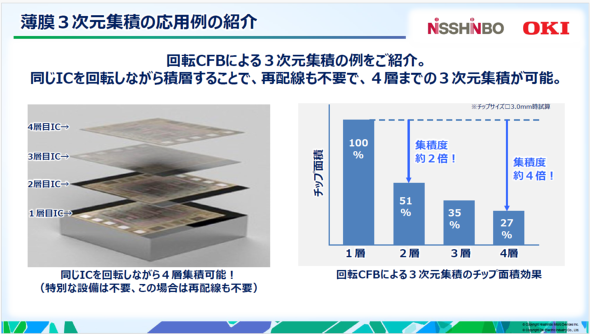

なお、CFBは、複数の薄膜アナログICを90度回転させながら積層していくことも可能だ。90度ずつ回転して積層していくと、ボンディングパッドが重ならないので、ボンディングワイヤを引き出すことができる。

同じアナログICを回転させて積層することも可能。図版に「4層まで」とあるのは、ボンディングパッドが重ならずに積層できるのが4層(90度×4=360度)まで、という意味で、技術的な制約があるからではない[クリックで拡大] 出所:OKI/日清紡マイクロデバイス

同じアナログICを回転させて積層することも可能。図版に「4層まで」とあるのは、ボンディングパッドが重ならずに積層できるのが4層(90度×4=360度)まで、という意味で、技術的な制約があるからではない[クリックで拡大] 出所:OKI/日清紡マイクロデバイスCopyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増