EE Times Japan >

テスト/計測 >

3D統合では正確な半導体検査が必須に:歩留まりにも直結(2/3 ページ)

» 2024年11月19日 14時30分 公開

[Kai Beckmann(Merck),EE Times]

「ムーアの法則」に連動するインターコネクト密度

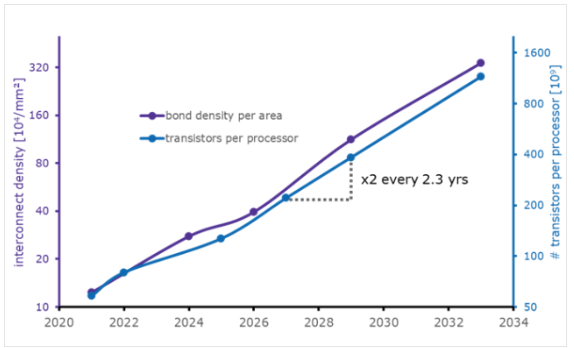

前述のような傾向は、経験的に観測されるだけでなく、図1が示すように定量的にも示されている。

プロセッサ当たりのトランジスタ数は2〜3年ごとに倍増し、古典的なムーアの法則を順守している。興味深いことに、ほぼ同じ割合で増加しているもう1つの指標となっているのが、インターコネクト密度だ。ムーアの法則は1970年代にさかのぼることができるが、インターコネクトは、増加の一途にある半導体チップの帯域幅需要によってもたらされた最近の傾向であり、AIにとって最大の課題の一つになっている。

これらは異なる基準であるにもかかわらず、半導体性能が向上すると、必然的に密接に関連することになる。フロントエンドとバックエンドでは、最先端技術の進展はどちらか一方に依存するためだ。

半導体チップのさまざまな部分を接続するインターコネクト密度が高まることで、複雑性はさらに増す。半導体チップが3Dアーキテクチャへと移行するに伴い、インターコネクトの密度はトランジスタ数と同じくらい重要になっている。インターコネクト密度が高くなれば、AIアクセラレーターやSiP(System-in-Package)ソリューションにとって不可欠なデータ伝送速度も速くなる。だが、エネルギー効率を犠牲にすることなくインターコネクトの数を増加させるには、高性能材料と精度の高い製造技術が必要だ。こうした分野で重要な役割を担うのが計測である。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR

紫がインターコネクト密度で、青がトランジスタの集積度 出所:TSMC

紫がインターコネクト密度で、青がトランジスタの集積度 出所:TSMC