TSV/RDL受託開発で「次のNVIDIA」登場を加速 コネクテックジャパン:量産なしでも受託可能(1/2 ページ)

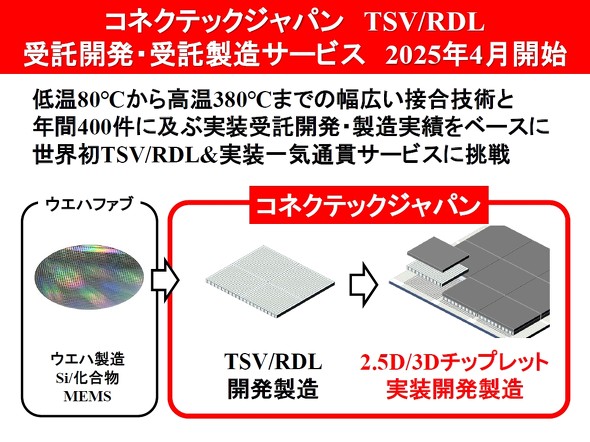

コネクテックジャパンは、TSV(貫通ビア)/RDL(再配線層)の受託開発と受託製造を一気通貫で行うサービスを2025年4月に開始する。量産の有無にかかわらず利用が可能で、ウエハー1枚からでも請け負う。

半導体やセンサー、MEMSなどの実装受託開発サービスを手掛けるコネクテックジャパンは、TSV(貫通ビア)/RDL(再配線層)の受託開発と製造、実装を一気通貫で行うサービスを2025年4月に開始する。チップレット集積に欠かせないTSVとRDLの開発/製造サービスを提供することで、AI(人工知能)用をはじめとする高性能半導体デバイスの開発を加速することが狙いだ。

「1円も集められなかった4年間」

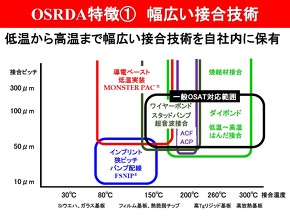

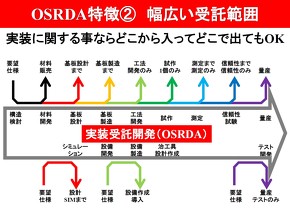

2009年11月に設立されたコネクテックジャパンは、ことしで設立15周年を迎えた。同社代表取締役会長の平田勝則氏は、「最初の4年間は資金を1円も集められなかった。日本列島をくまなく周って3000社を訪ね、顧客やパートナーからいろいろなアイデアをいただいたことで、15年間ビジネスを継続できた」と振り返る。同社は、低温導電ペースト技術、Cu(銅)ピラー/はんだバンプ接合技術など、低温から高温までの接合技術を生かした半導体実装受託開発、製造サービス「OSRDA(Outsourced Semiconductor Research Development & Assembly)」を提供。現在は年間400件に上るプロジェクトを手掛けている。

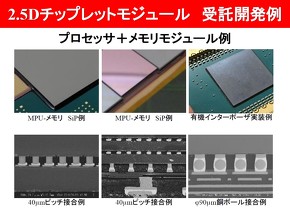

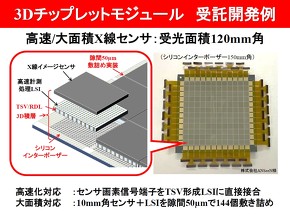

その同社で、ここ数年、急激に案件が増えているのがチップレットだ。受託件数の内訳では、全体の36%をチップレット関連が占めるという。「当社の半導体受託開発では引き合いの多くがシステムLSI以外になっている。1チップで付加価値を引き出せる時代では既にないという印象を持っている」(平田氏)

チップレット集積の2つの課題

半導体の高性能化、高機能化の手段として注目されるチップレット集積だが、課題もある。一つは熱や応力に対する脆弱性だ。化合物半導体のチップレットをシリコンインターポーザーに実装する際などに、硬度や熱膨張係数のミスマッチを解消する必要がある。コネクテックジャパンは、半導体を80℃の低温で実装する独自技術「MONSTER PAC」を用いて、この課題を解決できるとする。

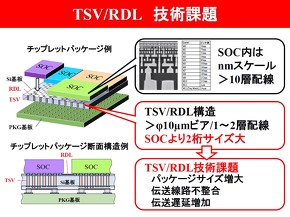

もう一つの課題がTSV/RDLの微細化だ。チップレットの実装には、チップレット間を接続するTSVとRDLが欠かせない。だが、「この分野では、ここ十数年ほど技術進化がやや止まっている。微細化、薄膜化、多層化などにおいて足踏み状態が続いている」と平田氏は指摘する。

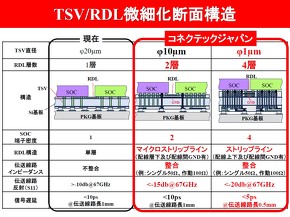

コネクテックジャパン 取締役 専務執行役員 先端開発本部長の下石坂望氏は、「SoC(System on Chip)ではナノメートルスケールで10層以上の多層配線が当然のようになっているが、それを実装するシリコンインターポーザー側は、そこまで到達していない。10年以上前から、TSVのビア直径(φ)を1μmにする必要があるといわれているが、実現せずに今に至る」と説明する。「φ10μmなどが発表されていても、現実では見たことがない」(平田氏)。配線層についても1〜2層が現状だ。

コネクテックジャパンは、2層/4層の配線層数と、φ10μm、φ1μmのTSV直径を目指す。「実現できそうだという手応えはつかんだ」と平田氏は強調する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

コネクテックジャパン 代表取締役会長の平田勝則氏

コネクテックジャパン 代表取締役会長の平田勝則氏