NORフラッシュにもAI需要の波、迫る供給危機:30%の値上げの可能性も(2/2 ページ)

期待が高まる3D NORフラッシュ

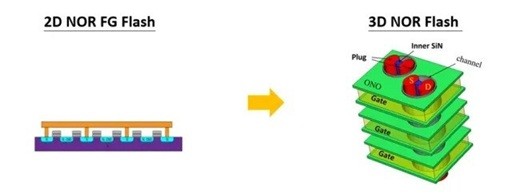

3D NOR型フラッシュは、メモリセルを垂直にスタックすることで、2D NORのプレーナ型アーキテクチャに特有のスケーラビリティの問題を克服する。垂直スタックは、フットプリントを大きくせずにストレージを高密度化でき、eMMC(embedded Multi Media Card)やNANDのような複数のストレージデバイスの必要性を低減する。また3D NORは、レイテンシを短縮し、ブート性能を向上させるので、ほぼ瞬時に保存データにアクセスする必要があるアプリケーション向けには非常に重要だ。

2D NORの最大密度が512Mビットであるのに対し、3D NOR型フラッシュは密度を8倍に向上させ、単一のダイで512Mビットを達成する。また、200MHzのDTR(Double Transfer Rate)を採用し、大量データへの高速アクセスが必要なAIアプリケーション向けに、高速データ伝送を提供する。

しかし、3D NOR型フラッシュは新時代の大容量組み込みストレージとして期待される一方で、幅広い規模での実用化はまだ何年も先になる見込みだ。特に現在では、大手メモリメーカーがNOR型フラッシュ技術への投資を行っていないということもある。

大手サプライヤーであるMacronixは、2026年後半には3D NOR型フラッシュデバイスのサンプル出荷を開始し、2027年には本格量産を予定しているという。業界はそれまでは、2D NOR型フラッシュの供給危機に対応しなければならない。NOR型フラッシュは、DRAMやNANDと比べると規模が小さい分野だが、AI設計における需要の急増や、HBM需要の増大による生産能力の大規模な再編などを受け、注目すべきメモリ技術の1つとなっている。

【翻訳:田中留美、編集:EE Times Japan】

関連記事

メモリとストレージの動向を示す11個のキーワード(後編)

メモリとストレージの動向を示す11個のキーワード(後編)

メモリとストレージの市場アナリストとして知られるJim Handy氏の講演を紹介するシリーズの後編。メモリのファウンドリー事業の可能性や、決して新しくはないプロセッサインメモリ技術、ストレージ化する半導体メモリなどを取り上げる。 2030年の半導体メモリ市場は平均10%成長で3020億米ドルへ

2030年の半導体メモリ市場は平均10%成長で3020億米ドルへ

2025年8月に開催された「FMS(the Future of Memory and Storage)」の一般講演を紹介する。今回は、Yole Groupのシニアアナリストがメモリ市場の概況を解説する講演を取り上げる。 新興メモリの普及、狙いはNORフラッシュの置き換え

新興メモリの普及、狙いはNORフラッシュの置き換え

磁気抵抗メモリ(MRAM)/抵抗変化型メモリ(ReRAM)などの新興メモリは、宇宙や防衛など、特殊な用途だけでなく、車載などでも採用できる準備が整ってきた。 「業界初」SamsungがHBM4の量産、出荷開始

「業界初」SamsungがHBM4の量産、出荷開始

Samsung Electronicsが「業界初」(同社)となる広帯域メモリ(HBM)の最新世代「HBM4」の量産開始および商用製品の出荷を発表した。競争が激化するAIデータセンター向けHBM市場で先行確保を狙う。 欧州に半導体サプライチェーンは戻るか ドイツ発メモリ新興が鍵

欧州に半導体サプライチェーンは戻るか ドイツ発メモリ新興が鍵

世界各国で自国内への半導体製造回帰への動きが強まり、地政学的緊張から「今が最後のチャンス」とも目される中、欧州に不足しているのはメモリ製造だ。独自技術を有するドイツの新興企業に注目が集まっている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- 加賀電子が新光商事にTOB、完全子会社化へ

- 地政学が変えるメモリ調達戦略 「安く買う」だけでは危険