「AIの進化」に追い付けない半導体開発 解決の道筋は:「最初に規模を拡張」に潜むわな(2/3 ページ)

熟練エンジニア不足にAIで対応する

UIUCが高性能ソリューションに取り組んでいる一方で、欧州の研究者たちは、もう1つの別の課題である「熟練ハードウェアエンジニアの不足」に、AIを使って対応しているところだ。バルセロナスーパーコンピューティングセンター(BSC:Barcelona Supercomputing Center)の主席リサーチエンジニアであるTeresa Cervero氏は「現代のチップ設計が複雑なために、学生やスタートアップ、小規模企業にとっての参入障壁がとてつもなく高くなっている」と強調した。

Cervero氏は、カンファレンスで行われた米国EE Timesのインタビューで「欧州では、専門的なスキルを持つ人材が多くはないため、その問題を改善する必要がある。われわれは、エンジニアたちが低レベルの詳細に入り込むことを恐れなくても済むよう、参入障壁を下げたいと考えている」と述べる。

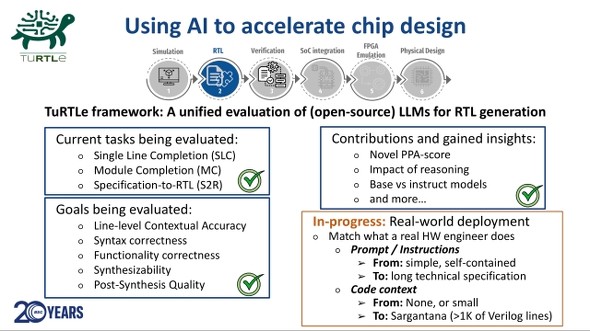

BSCの研究者たちは、オープンソースのRISC-Vプロセッサ向けの設計プロセスにLLMを追加しているという。大手技術メーカーの閉じられた「ブラックボックス」モデルではなく、容易にアクセス可能なオープンソースのツールを使用するのだ。Cervero氏は、LLMが、RTLコードや、意図した通りにチップを確実に機能させるためのSystemVerilogチェックなどを生成することにより、どのようにサポートしているのかを説明した。

しかし同氏は、完全な自動化については期待を抑え、慎重な姿勢を見せた。「エンジニアリングワークを置き換えるのではなく、ただ追加のツールを得るということだ。ただ単に『このプロンプトで、私のためにチップ全体を設計してほしい』と言うことはできない。自分でそれを導く必要がある。チップの中に入れれば完成するが、修正はできないのだ」と述べる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 加賀電子が新光商事にTOB、完全子会社化へ

- SiC LSIの事業化に挑む 28年以降ADCのサンプル出荷へ

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- Cerebrasが上場 NVIDIA対抗馬の「試金石」となるか

- AIの「トンデモ判断」で本番DBが全飛び! 他山の石にしたいAIコーディングの落とし穴

- サンケン電気26年3月期は赤字転落 中国の「自前主義」響く

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

Teresa Cervero氏 出所:BSC

Teresa Cervero氏 出所:BSC