先進パッケージのシステム・製造協調最適化(STCO):福田昭のデバイス通信(508) TSMCが解説する最新のパッケージング技術(5)

「IEDM 2025」におけるTSMCの講演内容を紹介する。今回は「System-Technology Co-Optimization (STCO)(システム・製造協調最適化)」を解説する。

AI/HPCシステムのハードウェア構成

2025年12月に開催された国際学会IEDMのショートコース(技術解説)で、シリコンファウンドリー最大手のTSMCが最新のパッケージング技術を説明した。講演のタイトルは「Advanced Packaging and Chiplet Technologies for AI and HPC Applications(AIおよびHPCに向けた先端パッケージング技術と先端チップレット技術)」、講演者はAdvanced Package Integration Division R&DのディレクターをつとめるJames Chen氏である。大変に参考となる内容だったので、その一部をシリーズでご紹介している。ただし講演内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演内容を筆者が適宜、補足してある。あらかじめご了承されたい。

![講演「Advanced Packaging and Chiplet Technologies for AI and HPC Applications(AIおよびHPCに向けた先端パッケージング技術と先端チップレット技術)」のアウトライン[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)](https://image.itmedia.co.jp/ee/articles/2602/27/mm260227_device00.jpg) 講演「Advanced Packaging and Chiplet Technologies for AI and HPC Applications(AIおよびHPCに向けた先端パッケージング技術と先端チップレット技術)」のアウトライン[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

講演「Advanced Packaging and Chiplet Technologies for AI and HPC Applications(AIおよびHPCに向けた先端パッケージング技術と先端チップレット技術)」のアウトライン[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)タイトルスライドの次に示されたアウトラインは、「AI and HPC Market Outlook(AIとHPCの市場を展望)」「Advanced Package Technology Evolutions(先進パッケージ技術の進化)」「System-Technology Co-Optimization (STCO)(システムと製造の協調最適化)」「Emerging Advanced package technology(次世代の先進パッケージ技術)」「Summary(まとめ)」となっていた。

本シリーズの前回は、アウトラインの第2項「Advanced Package Technology Evolutions(先進パッケージ技術の進化)」に相当する部分を述べた。今回からはアウトラインの第3項「System-Technology Co-Optimization (STCO)(システム・製造協調最適化)」に相当する部分の説明を始めよう。

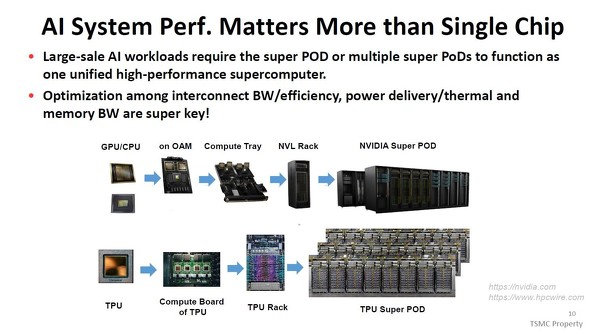

本シリーズの第2回「モノリシック集積の限界を超えるヘテロジニアス集積化」で述べたように、シングルチップではもはや、AI(人工知能)やHPC(高性能)などの応用分野が要求する性能仕様には応えられない。先進パッケージングによるチップレット化および広帯域メモリ(HBM)の混載、ボードレベルでのモジュール化、複数のモジュールを搭載したラック、複数のラックを収容したPOD(Performance Optimized Datacenter)へとプロセッサ数やメモリ容量などを著しく拡大することで、AIとHPCの高い性能要求に応えている。

AI(人工知能)システムのハードウェア構成。左から右へ、すなわち先進パッケージング、ボードレベルでのモジュール化、複数のモジュールを搭載したラック、複数のラックを収容したPOD(Performance Optimized Datacenter)あるいは複数のPODへと集積規模を拡大することで、システムを構成している[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

AI(人工知能)システムのハードウェア構成。左から右へ、すなわち先進パッケージング、ボードレベルでのモジュール化、複数のモジュールを搭載したラック、複数のラックを収容したPOD(Performance Optimized Datacenter)あるいは複数のPODへと集積規模を拡大することで、システムを構成している[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)システム化で重要なカギとなるのが、相互接続の帯域幅とその効率、電源分配、放熱(冷却)、メモリの帯域幅などだ。そこでSTCO(システム・製造協調最適化)が必要となる。

帯域幅密度、拡張性、消費エネルギー、放熱、電源供給などに配慮

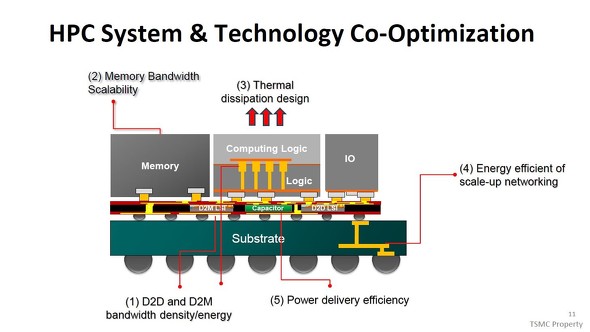

STCOは先進パッケージングの設計・製造段階から始まっている。ここでは「CoWoS-L(LSI+RDL interposer)」タイプの先進パッケージを例に考える。

STCO(システムと製造の協調最適化)で考慮すべき事柄。先進パッケージ「CoWoS-L(LSI+RDL interposer)」の例[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

STCO(システムと製造の協調最適化)で考慮すべき事柄。先進パッケージ「CoWoS-L(LSI+RDL interposer)」の例[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)最初(1)はロジックのミニダイ間接続(D2D)とロジックとメモリの接続(D2M)である。接続帯域幅の密度(単位長当たり)と消費エネルギーが指標となる。次(2)はメモリ入出力帯域幅の拡張性(スケーラビリティ)である。それから(3)消費電力および放熱の設計が重要となる。プロセッサは消費電力密度が高く、放熱設計が欠かせない。

ボードレベルでは複数のCoWoS-Lパッケージを相互接続する。ここでは(4)データ転送による消費エネルギーの効率を高めることが求められる。そして(5)パッケージ内に電源を効率的に供給する。

これらのことから、帯域幅密度と拡張性、エネルギー効率が基本的に考慮すべき事柄であることが分かる。

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

インターポーザに複数のシリコンダイを近接して並べる2.5次元集積化

インターポーザに複数のシリコンダイを近接して並べる2.5次元集積化

前回に続き、「IEDM 2025」におけるTSMCの講演内容を紹介する。TSMCの2.5次元パッケージング技術「CoWoS(Chip on Wafer on Substrate)」において、インターポーザを低コスト化する技術を解説する。 複数のミニダイ(チップレット)を1つのパッケージに収容する

複数のミニダイ(チップレット)を1つのパッケージに収容する

2025年12月に開催された国際学会IEDMにおける、TSMCの講演を解説するシリーズ。今回は、前回に続き、「先進パッケージ技術の進化」を取り上げる。分割した複数のミニダイを同一パッケージに収容する際の、3つの接続手法を解説する。 AIサーバの高性能化に不可欠となった先進パッケージング技術

AIサーバの高性能化に不可欠となった先進パッケージング技術

2025年12月の国際学会IEDMで、TSMCが最新のパッケージング技術について講演した。本シリーズは、その内容の一部を紹介する。 メモリとストレージの動向を示す11個のキーワード(前編)

メモリとストレージの動向を示す11個のキーワード(前編)

2025年8月に開催された「FMS」の講演を紹介するシリーズ。今回はメモリとストレージの市場アナリストとして知られるJim Handy氏の講演を前後編でご紹介する。 2026年のHBM市況、カギを握るのは最新世代「HBM4」

2026年のHBM市況、カギを握るのは最新世代「HBM4」

2025年8月に開催された「FMS(the Future of Memory and Storage)」の一般講演を紹介するシリーズ。今回はTrendForceのアナリストであるEllie Wang氏の講演を取り上げる。広帯域メモリ(HBM)の生産能力や容量、価格を予測する。 創刊前の20年間(1985年〜2005年)で最も驚いたこと:1985年の「不可能」二題

創刊前の20年間(1985年〜2005年)で最も驚いたこと:1985年の「不可能」二題

EE Times Japan 創刊20周年に合わせて、半導体業界を長年見てきたジャーナリストの皆さまや、EE Times Japanで記事を執筆していただいている方からの特別寄稿を掲載しています。今回は、40年以上にわたり半導体技術/電子技術を見守り、フリーの技術ジャーナリストとして活躍されている福田昭氏にご寄稿いただきます。EE Times Japan創刊からさらに20年さかのぼり、1985年の話からスタートします。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング