AI/HPCシステムのメモリ/ストレージ階層とHBMの高性能化:福田昭のデバイス通信(510) TSMCが解説する最新のパッケージング技術(7)(2/2 ページ)

過去11年でHBMの記憶容量は6倍、帯域幅は9.8倍に

ここからは、ハイエンドAI/HPCシステムの主記憶であるHBMを解説しよう。HBMの基本的な考え方は、入出力信号のバス幅を広くすることで高い帯域幅を確保すること、専用のDRAMダイを垂直方向に積み重ねることで記憶容量を大きくすることにある。バス幅は1024ビット(物理的には1024本の入出力電極)と極めて広い。入出力電極1本のデータ転送速度(ビット/秒)に対し、バイト換算の帯域幅(バイト/秒)は128倍に達する。

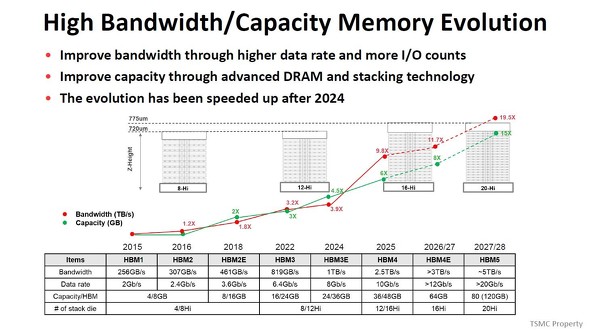

1個のHBMモジュールは、最下層のロジックダイ(「ベースダイ」)と、その上に積み重ねる専用DRAMダイ(「コアダイ」)で構成する。コアダイの積層枚数は当初、4枚あるいは8枚だった(HBM1世代とHBM2世代、HBM2E世代)。その後は8枚あるいは12枚(HBM3世代とHBM3E世代)、12枚あるいは16枚(HBM4世代)と積層枚数を増やしてきた。並行してコアダイの記憶容量を拡大しており、モジュール当たりの記憶容量は当初のHBM1/2世代の最大8Gバイトから、最新のHBM4世代では最大48Gバイトと6倍に増加している。

また入出力電極当たりのデータ転送速度は第1世代のHBM1で2Gビット/秒だったのが、最新世代のHBM4では5倍の10Gビット/秒に向上した。さらにHBM4世代ではバス幅をそれまでの2倍である2048ビット(物理的には2048本の入出力電極)に拡大した。このバス幅拡大などによって帯域幅は最大で前世代のHBM3Eから2.5倍に高めている。

HBM(High Bandwidth Memory)の開発ロードマップ。最新世代は「HBM4」である。「HBM4E」以降は推定。[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

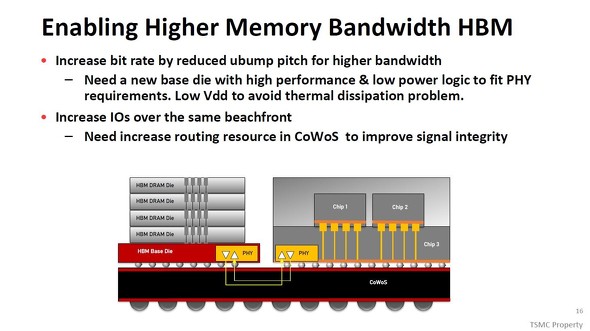

HBM(High Bandwidth Memory)の開発ロードマップ。最新世代は「HBM4」である。「HBM4E」以降は推定。[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから) HBM(High Bandwidth Memory)の帯域幅拡張手法。入出力電極当たりのデータ転送速度を高める、電極ピッチを狭める、電源電圧を下げる、入出力電極数を増やすといった要素技術を駆使する[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

HBM(High Bandwidth Memory)の帯域幅拡張手法。入出力電極当たりのデータ転送速度を高める、電極ピッチを狭める、電源電圧を下げる、入出力電極数を増やすといった要素技術を駆使する[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)パッケージング技術におけるHBMの特徴は、コアダイとロジックダイにシリコン貫通電極(TSV:Through Silicon Via)を設けたことだろう。軽く1000本を超えるTSVがダイを貫通する。HBMモジュールの断面構造図を見ると、TSVの位置はいずれも中央にある。これは偶然ではない。

国際学会で発表されたHBMダイのレイアウト図面では、TSV領域は中央にあり、その周辺には配線しかない。トランジスタや受動素子などは少し離れてレイアウトしてある。これはTSVによる歪みの影響を緩和するためだ。TSVはダイ間の接続距離を極限まで短くできるものの、シリコン面積の効率(記憶密度)は良くない。HBMモジュールは供給可能なベンダーが限られていることから、低くないコストを上回る価格で取引きされている。売り上げと利益への貢献度は高い。

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

先進パッケージのシステム・製造協調最適化(STCO)

先進パッケージのシステム・製造協調最適化(STCO)

「IEDM 2025」におけるTSMCの講演内容を紹介する。今回は「System-Technology Co-Optimization (STCO)(システム・製造協調最適化)」を解説する。 インターポーザに複数のシリコンダイを近接して並べる2.5次元集積化

インターポーザに複数のシリコンダイを近接して並べる2.5次元集積化

前回に続き、「IEDM 2025」におけるTSMCの講演内容を紹介する。TSMCの2.5次元パッケージング技術「CoWoS(Chip on Wafer on Substrate)」において、インターポーザを低コスト化する技術を解説する。 複数のミニダイ(チップレット)を1つのパッケージに収容する

複数のミニダイ(チップレット)を1つのパッケージに収容する

2025年12月に開催された国際学会IEDMにおける、TSMCの講演を解説するシリーズ。今回は、前回に続き、「先進パッケージ技術の進化」を取り上げる。分割した複数のミニダイを同一パッケージに収容する際の、3つの接続手法を解説する。 AIサーバの高性能化に不可欠となった先進パッケージング技術

AIサーバの高性能化に不可欠となった先進パッケージング技術

2025年12月の国際学会IEDMで、TSMCが最新のパッケージング技術について講演した。本シリーズは、その内容の一部を紹介する。 メモリとストレージの動向を示す11個のキーワード(前編)

メモリとストレージの動向を示す11個のキーワード(前編)

2025年8月に開催された「FMS」の講演を紹介するシリーズ。今回はメモリとストレージの市場アナリストとして知られるJim Handy氏の講演を前後編でご紹介する。 2026年のHBM市況、カギを握るのは最新世代「HBM4」

2026年のHBM市況、カギを握るのは最新世代「HBM4」

2025年8月に開催された「FMS(the Future of Memory and Storage)」の一般講演を紹介するシリーズ。今回はTrendForceのアナリストであるEllie Wang氏の講演を取り上げる。広帯域メモリ(HBM)の生産能力や容量、価格を予測する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- ルネサス26年1Qは増収増益 車載/AI好調で「足元は当面強い」

- 「Rapidusの隣」に光電融合パッケージ開発拠点、28年度の完成目指す

- 「3社のパワー半導体事業を切り出し合弁設立したい」三菱電機社長