微細化の限界に挑む、Siと新材料の融合で新たな展望も:プロセス技術(3/10 ページ)

幾何学的スケーリングの限界

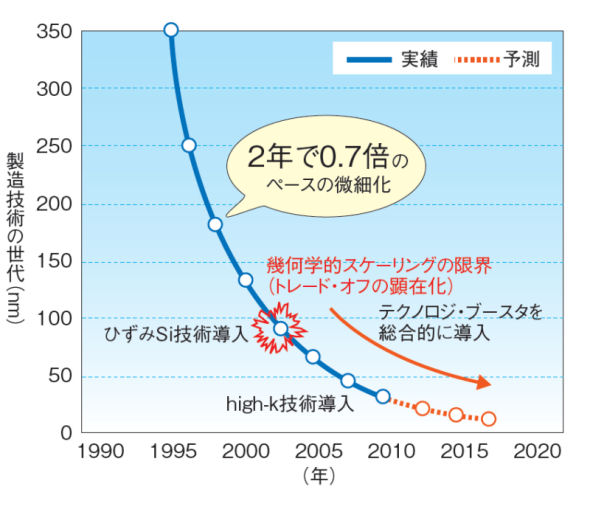

微細化は限界だと幾度となく言われてきたものの、半導体ベンダー各社はその限界を乗り越えてきた。しかし、2000 年代に入り、製造技術が90nm世代に突入するとスケーリング則に従った微細化が極端に難しくなってきた(図3)。

図3 幾何学的スケーリングに従った微細化の流れ 90nm世代以降、MOS FETの寸法をひたすら縮小する幾何学的スケーリングによる性能向上は難しくなってきた。現在では、ひずみSiやhigh-k/ 金属ゲートといった「テクノロジ・ブースタ」の力を借りて、微細化を進めている。

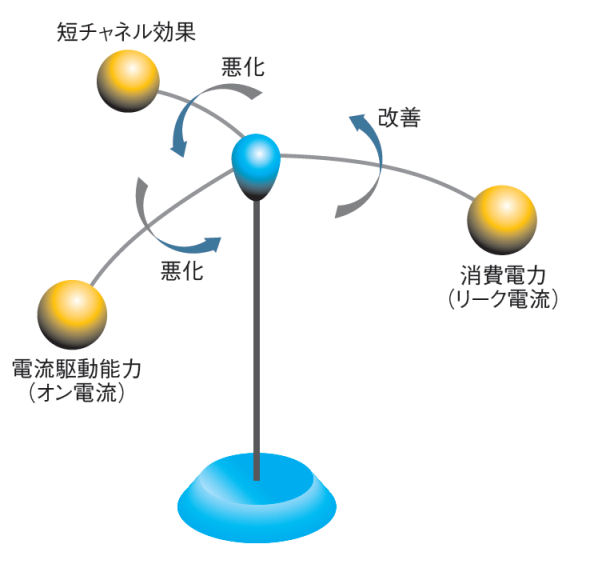

図3 幾何学的スケーリングに従った微細化の流れ 90nm世代以降、MOS FETの寸法をひたすら縮小する幾何学的スケーリングによる性能向上は難しくなってきた。現在では、ひずみSiやhigh-k/ 金属ゲートといった「テクノロジ・ブースタ」の力を借りて、微細化を進めている。ロジック回路を構成するMOS FETには、いくつかの評価項目がある。例えば、電流駆動能力が高く、オン時とオフ時のドレイン電流の差が大きい、低い駆動電圧で動作するといったものだ。微細化が進展するにつれて、これらの評価項目と密接に関連した、「短チャネル効果」と「消費電力(リーク電流)」、「オン電流(電流駆動能力)」という3つの項目を、同時に改善するのが難しくなってきたのである(図4)。

図4 トレードオフの関係が顕在化 MOS FETの性能に密接に関連する「短チャネル効果」と「消費電力」、「電流駆動能力」はトレードオフの関係にある。微細化を進め、どれかを改善しようとすると、ほかの2つが悪化し、バランスが崩れてしまう。

図4 トレードオフの関係が顕在化 MOS FETの性能に密接に関連する「短チャネル効果」と「消費電力」、「電流駆動能力」はトレードオフの関係にある。微細化を進め、どれかを改善しようとすると、ほかの2つが悪化し、バランスが崩れてしまう。短チャネル効果とは、MOS FETのゲート長を微細化したときに生じる現象である*2)。この現象によって、トランジスタのしきい値電圧(Vth)が小さくなって、「サブスレッショルド・リーク」と呼ぶ漏れ電流が増大し、トランジスタの性能を表す指標である「Sファクタ」*3)が大きくなるなどの悪影響を生む。

短チャネル効果を防ぐには、基板の不純物濃度を高めることが有効だ。ところが、不純物濃度を高めることは、移動度の低下やリーク電流の増大を招く。オン電流(電流駆動能力)は、ソース端でのキャリア密度とキャリアの移動度の積で決まるため、移動度が低下すると、電流駆動能力が下がってしまう。

スケーリング則に従ってゲート絶縁膜を薄くすることも難しくなってきた。ゲート絶縁膜を薄くすると静電容量が大きくなり、オン電流は増える*4)。ところが、絶縁膜が薄くなりすぎると、トンネル効果によってリーク電流が急激に増えてしまう。

以上のように、3つの項目のうち1つを改善しようとするとほかの項目が劣化し、バランスが崩れてしまう。素子の寸法を縮小していくことで、MOS FETの性能を改善する「幾何学的スケーリング」だけでは、もはや性能の向上を見込めなくなったのである。

「Q=CV」となる。Vはゲート電圧、Cはゲート絶縁膜の容量である。ゲート絶縁膜を薄くしてCを増やせば、オン電流(ドレイン電流)を高められる。

「テクノロジ・ブースタ」が必須に

そこで現在、MOS FETの集積度を上げつつ性能を向上させるために、Si(シリコン)基板上にSi 以外の材料を使ったMOS FETを配置したり、MOS FETの構造をまったく新しくするなどの対策が進んでいる。

もちろん、Si以外の材料を使った半導体製品は古くから存在する。例えば、基板にもFET 部にもGaAs(ガリウム・ヒ素)などの化合物を使った半導体は、Si材料を使ったものよりも高速に動作する。ただ、高価であるなどの欠点がある。最近では、Siを完全に排除するのではなく、Si基板を使い、これまでの製造技術や設計資産を最大限活用しながら、微細化をさらに推し進めようとする研究が盛んだ。Siをまったく使わない化合物半導体デバイスとは根本的に異なり、Si材料のロジック回路にSiとは異なる新材料を組み込む。

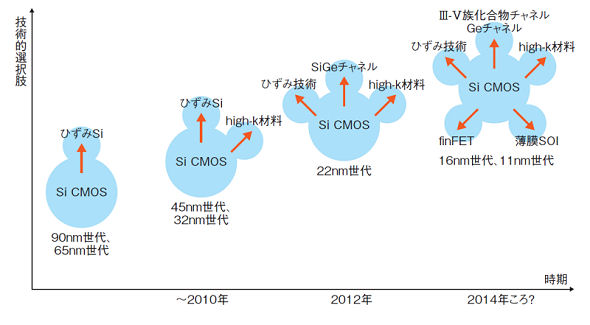

Si材料を用いたMOS FETの性能を向上させ、微細化を押し進めるための新材料や新構造を「テクノロジ・ブースタ」と呼ぶ*5)。いくつもの提案があり、すでに製品への導入が進んでいる。複数のテクノロジ・ブースタを組み合わせて、微細化を極限まで推し進めようというのが業界の共通認識だ(図5)。

図5 テクノロジ・ブースタを続々導入 集積度を高めつつ、性能を向上させるため、さまざまなテクノロジ・ブースタの導入が進む。16nm世代または11nm世代では、Geチャネルにひずみ技術を組み合わせることも検討されている。

図5 テクノロジ・ブースタを続々導入 集積度を高めつつ、性能を向上させるため、さまざまなテクノロジ・ブースタの導入が進む。16nm世代または11nm世代では、Geチャネルにひずみ技術を組み合わせることも検討されている。すでに、ゲート絶縁膜に使う高誘電率(high-k)材料や、ひずみSi技術の導入が進んでいる。high-k材料を使えば、ゲート絶縁膜を薄くしても、電流駆動性能をそのままに維持し、短チャネル効果を抑えつつリーク電流を抑制できる。Intel 社は、high-k 材料を

45nm世代で初めて導入し、続く32nm世代にも採用した。「high-k 材料を採用した45nm世代は65nm世代に比べて、リーク電流が劇的に減った。p 型MOS FETなら1/1000、n型MOS FETでは1/25にまで減った」(同社)。

また、ひずみSiは、Si 結晶をひずませることで、キャリアの移動度を高める技術である。移動度を高めることで、電流駆動能力が向上し、高速動作が可能になる。同社は、90nm世代の製造技術にひずみSi技術を初導入した。その後、45nm 世代と32nm 世代にも引き続き導入している。ひずみSiのように、キャリアの移動度を高める材料(高移動度チャネル)としては、SiGe( シリコン・ゲルマニウム)やGe( ゲルマニウム)、III-V 族化合物、C(炭素)のみからなるグラフェンが候補に挙がる(高移動度チャネルの現在の開発状況については、別掲記事「さらなる微細化には不可欠、次世代高移動度チャネル」と、「Intel社の担当者が語る、III-V族は2015年に実用化へ」を参照)。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増