微細化の限界に挑む、Siと新材料の融合で新たな展望も:プロセス技術(7/10 ページ)

リーク電流を42%減

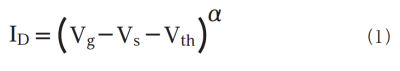

強誘電体の働きによってVthが変わることで、SRAMの動作安定性を示す静的雑音余裕(SNM:Static Noise Margin) や、Vthのばらつきに対する許容値(Vwindow)を広げられる(図4)。

Vwindowとは、SRAMを構成するn 型MOS FETのVthをグラフの横軸に、p型MOS FETのVthを縦軸にしたとき、リーク電流の許容値や書き込み/読み込み時の電圧限界といった観点でSRAMがきちんと動作する電圧範囲を示したものである。SNMやVwindowが広いことは、電源電圧を引き下げても、安定して動作させられることを意味する。

図4 SRAMの「バタフライ・カーブ」を不均等にできる 既存のSRAMと強誘電体SRAMの違いは、動作の安定度を表す「バタフライ・カーブ」に顕著に表れる。バタフライ・カーブとは、SRAMを構成する2つのインバータの入出力をグラフ化したもの。既存のSRAMでは、バタフライ・カーブは「1」または「0」の状態を示す2つの安定点に対して、SRAMの動作安定性を示す静的雑音余裕(SNM)は均等である。強誘電体SRAMでは、「1」または「0」の状態の違いでバタフライ・カーブの形状が変わり、SNMが広がる。出典:東京大学竹内研究室

図4 SRAMの「バタフライ・カーブ」を不均等にできる 既存のSRAMと強誘電体SRAMの違いは、動作の安定度を表す「バタフライ・カーブ」に顕著に表れる。バタフライ・カーブとは、SRAMを構成する2つのインバータの入出力をグラフ化したもの。既存のSRAMでは、バタフライ・カーブは「1」または「0」の状態を示す2つの安定点に対して、SRAMの動作安定性を示す静的雑音余裕(SNM)は均等である。強誘電体SRAMでは、「1」または「0」の状態の違いでバタフライ・カーブの形状が変わり、SNMが広がる。出典:東京大学竹内研究室竹内氏の研究グループでは、コンピュータを使ったシミュレーションと、実際に試作した強誘電体SRAMセルを使って、強誘電体SRAMの動作を解析した。Vthの変化幅が0.1Vで電源電圧が0.5Vの条件のとき、Vwindowは30mVから137mVに、SNMは、0.12Vから0.19Vに広がった。この結果、電源電圧を0.11V下げられ、動作時消費電力を32%、リーク電流を42%削減できる見通しだという。「現在、材料はそのままに製造技術を改善することで、例えばVwindowを100mVから110mVへ広げるべく、各メーカーが研究を進めている。これに対して、ゲートの材料を変えるだけで、Vwindowが劇的に変わる意義は大きい。電源電圧が1.2Vである現時点では、今回の技術のインパクトは薄いかもしれないが、電源電圧を0.4Vや0.5Vにまで下げる必要に迫られたとき、今回の提案が生きてくる」(竹内氏)。

SDDの研究から発展

竹内氏の研究グループは産業技術総合研究所と共同で、強誘電体を使ったデバイスの開発に取り組んできた。2008年5月には、メモリー・セルに強誘電体を使ったNAND型フラッシュ・メモリーの動作を検証したことを発表した。さらに、2009年6月には、1トランジスタ型の強誘電体メモリーをページ・バッファに適用したSSD(Solid State Drive)を提案している。このような経緯から、強誘電体をSRAMに使って、Vthを制御することに着眼した。

強誘電体を利用したNAND 型フラッシュ・メモリーとは異なり、強誘電体膜を薄くし、分極状態を高速に変えられる材料の開発が重要になる。なお、ロジック回路やDRAMといったLSIを構成しているいくつかの回路ブロックのうち、SRAMに注目した理由について同氏は、「LSIの回路ブロックのうち、SRAMが最も電源電圧を下げにくい。強誘電体を使うことで電源電圧を引き下げられる効果を広くアピールできるため、SRAMに注目した」と語った。面積の半分以上をSRAMが占めるLSIもある。LSI全体の消費電力を削減するには、SRAMの消費電力を下げることが効果的である。

SRAMを構成するMOS FETの数を増やすなど、回路構成を複雑にすることでVwindowやSNMを広げることも可能だが、チップ面積が増大してしまう。これに対して、強誘電体SRAMでは、SRAMを構成するMOS FETの数や回路構成、実装面積は従来と何ら変わらない*2)。

磁性体の抵抗変化を利用

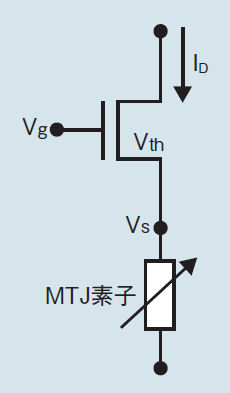

一方、東北大学電気通信研究所ブレインウェア実験施設新概念VLSIシステム研究部の教授である羽生貴弘氏の研究グループは、磁性材料に注目した研究を進めている。磁気トンネル接合(MTJ:Magnetic Tunnel Junction)素子を使って、Vthのばらつきに対する耐性を高めたロジック回路を設計しようというものだ。

MTJ素子とは、絶縁膜を2つの強磁性体膜で挟み込んだものである。一方の強磁性体膜は磁化の方向が変わりにくく、もう一方の強磁性膜は磁化の方向が変わりやすいものを使う。前者の強磁性膜を「固定層」、後者の強磁性膜を「自由層」と呼ぶ。外部から自由層の磁化方向を変えたとき、自由層の磁化方向が固定層の磁化方向と一致すると抵抗値が低くなり、磁化方向が一致していないときは抵抗が高くなる

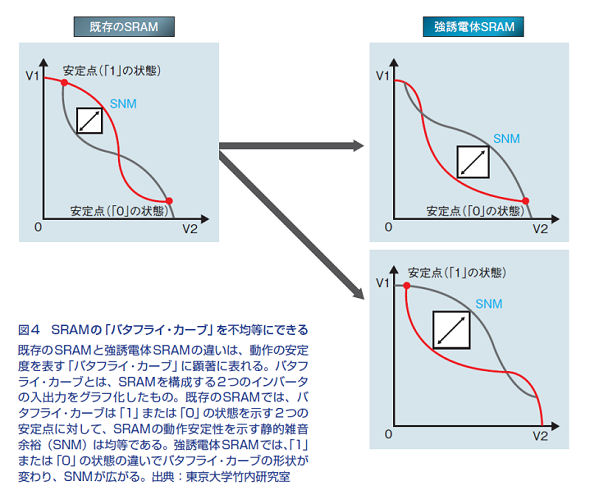

MTJ素子を使ってばらつき耐性を高めたロジック回路は、磁化方向によってMTJ素子の抵抗値が変わることをうまく利用したものだ。一般に、MOS FETのドレイン電流IDは以下のように表せる。

Vgがゲート電圧、Vsはソース電圧、αは1〜2の範囲の定数である。この(1)式から、Vthがばらつくと、これに伴ってIDもばらつくことが容易に分かる。そこで、MOS FETのVthが設定値と異なったとしても、VSを調整することで、IDの変化を補正しようというのが基本的な考え方である。MOS FETのソース側にMTJ素子を接続し、MTJ素子の抵抗値を変えれば、VSを調整できる(図5)。

図5 MTJ素子を使ったVthのばらつき対策 MOS FETのソース端にMTJ素子を接続する。Vthが設計値からずれたときに、MTJ素子の抵抗値を変えて、VSを調整することで、ドレイン電流IDの値を補正できる。

図5 MTJ素子を使ったVthのばらつき対策 MOS FETのソース端にMTJ素子を接続する。Vthが設計値からずれたときに、MTJ素子の抵抗値を変えて、VSを調整することで、ドレイン電流IDの値を補正できる。MTJ素子の抵抗値は、大小の2値しか取らないものの、VthがばらついたことによるIDの変化を抑制する効果は十分にあるとする。

電流モード多値回路で効果検証

すでに、試作回路を作成し、効果を検証済みだ*3)。高い精度の論理しきい値判定が必要な電流モード多値回路の比較回路に、MTJ素子を組み込んで、既存のロジック回路と性能を比較した。

電流モード多値回路は、多値信号を利用しているため、2値信号を使う回路よりも、高い精度の論理値判定が必要となる。90nm世代のCMOS製造技術を想定し、動作シミュレーションを実行したところ、Vthばらつきによる論理しきい値変動量を33%に低減できたとする。

「これまでは、製造技術を改善することで、Vthのばらつきを抑えることが主な対策だった。新材料と回路技術を融合させることで対策しようというのが我々のアイデアである。MTJ素子は、LSIの配線層に作り込むため、回路規模は増大しない」(羽生氏)。MTJ素子は、外部から電源を供給しなくても抵抗値の情報を保持し続け、書き換え耐性が高く、高速アクセスが可能という特徴がある。さらに、「LSIの配線層の上部に3次元的に積層でき、現在のMOS FETの製造技術と適合しやすいため、ロジック回路への導入に向く」(同氏)という。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円