2017年にミリ波レーダーはもっと安くなる? 富士通研がCMOSパワーアンプを開発:車載半導体

富士通研究所は、シリコンベースの半導体の製造に用いるCMOS技術でミリ波レーダーのパワーアンプを実現できる技術を開発した。ミリ波レーダーを使った自動車の予防安全システムの低価格化をさらに進展させられる可能性がある。2017年以降に量産車両への採用を目指す。

従来、自動車の予防安全システムなどに利用されているミリ波レーダーの高出力増幅器(パワーアンプ)には、高周波デバイスとして知られるガリウムヒ素(GaAs)系の化合物半導体が用いられていた。最近では、このGaAs系化合物半導体よりも安価に製造できるシリコンゲルマニウム(SiGe)ベースの半導体が採用されており、ミリ波レーダーの低価格化に貢献している(関連記事)。

しかし、SiGeベースの半導体よりも微細化が容易で量産規模も拡大しやすい、一般的なシリコン(Si)ベースの半導体技術を利用できれば、ミリ波レーダーのさらなる小型化とコスト削減が可能になる。

富士通研究所は2012年10月29日、Siベースの半導体技術によってミリ波レーダーのパワーアンプを実現するための新たな技術を開発したと発表した。2017年以降に、自動車への量産採用を目指す。

同社は2008年2月に、Siベースの半導体に用いるCMOS技術(90nmプロセス)で製造したパワーアンプを発表している。今回発表したのは、このCMOS技術で製造したパワーアンプを高出力化するためのパッケージング技術だ。

再配線技術を使ってパッケージング

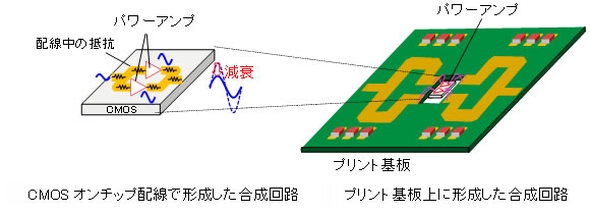

パワーアンプの高出力化では、複数個のパワーアンプを並列に配置して、その出力を合成する手法が知られている。CMOS技術でパワーアンプを製造できるのであれば、複数のパワーアンプ回路を1個のシリコンダイに集積すれば高出力化が達成できるはずだ。しかし、シリコンダイに集積すると、その配線層の薄さに由来する配線抵抗の大きさによって、パワーアンプ回路から出力する電力が出力部に到達するまでに約30%も減衰してしまうという問題があった。

一方、プリント基板上で出力合成回路を形成する場合、パワーアンプチップとプリント基板をつなぐ配線の加工や、ミリ波帯の高周波信号の伝達が難しい上に、パワーアンプを含めたミリ波レーダーモジュール全体のサイズが大きくなってしまう。

パワーアンプの出力合成回路。左の図は、1個のシリコンダイに集積する場合で、配線抵抗の大きさにより、合成時の出力の減衰も大きくなる。右の図は、プリント基板上で合成する場合で、配線の加工や信号伝達が難しく、サイズも大きくなってしまう。 出典:富士通

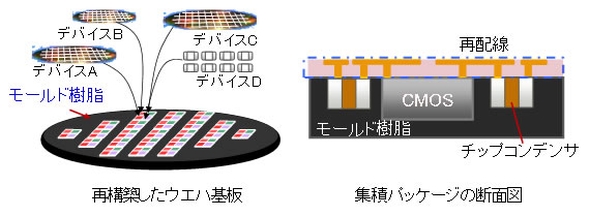

パワーアンプの出力合成回路。左の図は、1個のシリコンダイに集積する場合で、配線抵抗の大きさにより、合成時の出力の減衰も大きくなる。右の図は、プリント基板上で合成する場合で、配線の加工や信号伝達が難しく、サイズも大きくなってしまう。 出典:富士通そこで富士通研究所が採用したのが、再配線技術によってパワーアンプチップを並列化する手法である。再配線技術とは、半導体のパッケージング技術の1つで、半導体チップをモールド樹脂によりウェーハ状に再構築してから、CMOS技術の配線工程を適用して半導体チップ間の端子パターンを接続する。CMOS技術を使えるので、半導体チップ間の配線の微細加工が容易だ。さらに、半導体チップの他にチップコンデンサのような受動デバイスなども1個のパッケージの中に搭載できる。

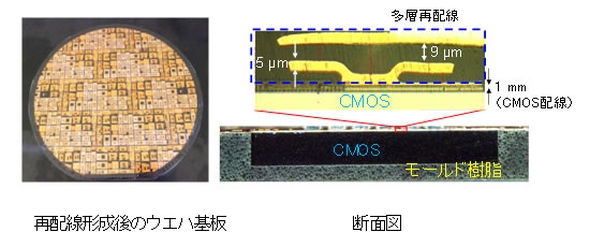

携帯電話機向けICのパッケージングに用いられている再配線技術では、配線層の層数は1層にとどまっていた。これに対して同社は、ミリ波帯の高周波信号が伝達できるように、複数の配線層を用いる多層再配線技術を開発。1個のシリコンダイにパワーアンプを集積する際に問題になっていた、配線層の薄さによる配線抵抗の大きさについては、5倍以上の厚みで配線層を形成できるようにして対応した。この他、多層再配線層に用いる絶縁膜や配線の幅を最適化するなどして、パワーアンプチップから出力する信号の減衰率を約10%に抑えたという。

左の写真は、富士通研究所の再配線技術を適用してウェーハ状に構築したパワーアンプモジュール。右の写真は、パワーアンプモジュールのパッケージの断面である。パワーアンプチップの最上層の配線の厚みは1μmであるのに対して、その上の多層再配線層は、配線の厚みが5μm、配線間の厚みが9μmとなっている。 出典:富士通

左の写真は、富士通研究所の再配線技術を適用してウェーハ状に構築したパワーアンプモジュール。右の写真は、パワーアンプモジュールのパッケージの断面である。パワーアンプチップの最上層の配線の厚みは1μmであるのに対して、その上の多層再配線層は、配線の厚みが5μm、配線間の厚みが9μmとなっている。 出典:富士通この技術を使って、出力電力が9mWの77GHz帯パワーアンプチップを4個並列に配置したパワーアンプモジュールを試作した。パワーアンプモジュールの出力電力は32mWで、合成効率は約88.9%となっている。減衰率は11.1%である。

なお、技術の詳細については、2012年10月28日(欧州時間)からオランダで開催される国際会議「EuMC 2012(European Microwave Conference 2012)」で発表する予定だ。

関連記事

三菱自動車も“止まる”プリクラッシュを採用、「EyeSight」よりも安価に

三菱自動車も“止まる”プリクラッシュを採用、「EyeSight」よりも安価に

三菱自動車は、「アウトランダー」の新モデルに、新開発の予防安全技術「e-Assist」を採用する。e-Assistは、自動ブレーキによって停車して衝突回避や衝突被害の軽減を可能にする「“止まる”プリクラッシュセーフティシステム」を搭載している。このe-Assistと、ボルボ、富士重工業、トヨタ自動車の止まるプリクラッシュを比較した。 3種類のレーダーとカメラで9つの安全機能を実現、マツダの「i-ACTIVSENSE」

3種類のレーダーとカメラで9つの安全機能を実現、マツダの「i-ACTIVSENSE」

マツダの先進安全技術「i-ACTIVSENSE」は、3種類のレーダーとカメラをセンサーデバイスとして用いることで9つの安全機能を実現している。新型「アテンザ」は、これら9つの安全機能を全て搭載する予定だ。 大衆車にも求められる「予防安全」

大衆車にも求められる「予防安全」

自動車の予防安全システムに用いられているセンサーのうち、事故回避に最も役立つものがミリ波レーダーである。この車載ミリ波レーダーについては、現在、大衆車にも広く搭載できるように低価格化を図るべく開発が進んでいる。本稿ではまず、車載ミリ波レーダーの特性や、使用されている周波数帯域に関する各国/地域の法規制について説明する。その上で、大手ティア1サプライヤや送受信ICを開発する半導体メーカーによる低価格化に向けた取り組みを紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- パワー停滞も光デバイス堅調、三菱電機の半導体部門

再配線技術の概要。左の図は、モールド樹脂を使って各種デバイスをウェーハ状に再構築する際のイメージである。右の図は、再配線技術を使ったパッケージの断面図。 出典:富士通

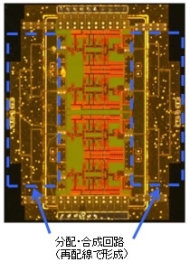

再配線技術の概要。左の図は、モールド樹脂を使って各種デバイスをウェーハ状に再構築する際のイメージである。右の図は、再配線技術を使ったパッケージの断面図。 出典:富士通 試作したパワーアンプモジュールのX線写真。青色の破線で示した部分が、再配線技術で形成したパワーアンプチップ出力の分配・合成回路である。 出典:富士通

試作したパワーアンプモジュールのX線写真。青色の破線で示した部分が、再配線技術で形成したパワーアンプチップ出力の分配・合成回路である。 出典:富士通