SiC-MOSFETの課題克服へ、新材料を用いたゲート絶縁膜で信頼性を向上:パワー半導体 SiCデバイス(2/2 ページ)

新たなゲート絶縁膜材料を採用

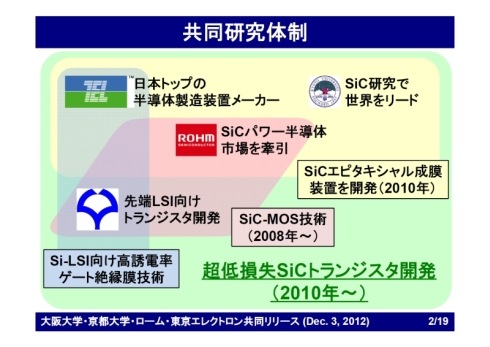

このSiC-MOSFETのゲート絶縁膜に関する課題を克服する技術を、大阪大学大学院工学研究科助教の細井卓治氏、教授の渡辺平司氏、京都大学大学院工学研究科教授の木本恒暢氏、ローム、東京エレクトロンによる共同研究チームが開発した。

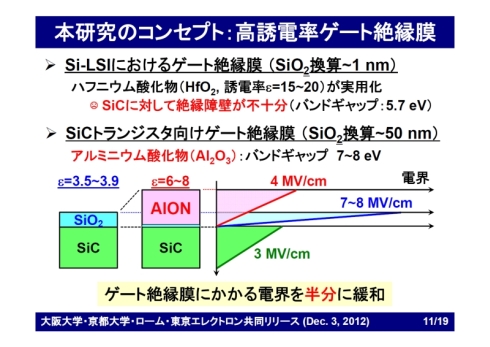

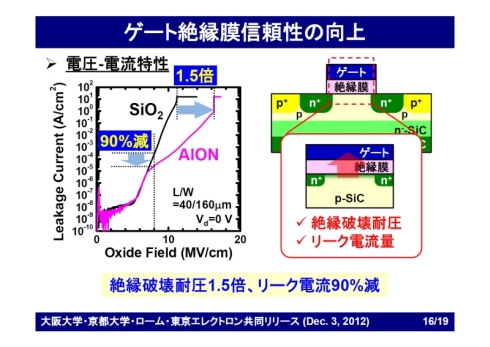

同技術では、SiC-MOSFETのゲート絶縁膜として、熱酸化法で成膜する酸化シリコンに替えて、デバイス性能と信頼性を高められるAlON(アルミニウム酸窒化物)を用いる。AlONのゲート絶縁膜は、動作時に印加される電界が4MV/cmと、酸化シリコンの半分に抑えられるので信頼性を確保しやすい。

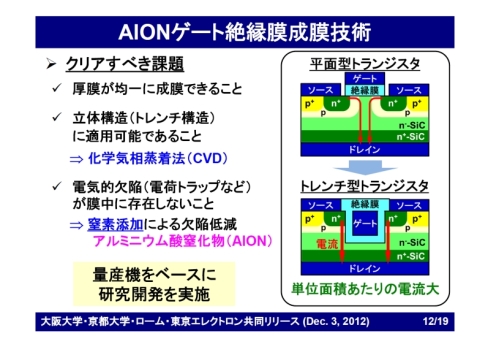

ただし、Siデバイスで量産実績のある熱酸化法で成膜する酸化シリコンと比べて、新技術となるAlONの成膜プロセスには、解決すべき課題が3つ存在する。1つ目は、酸化シリコンよりも膜厚が厚くなるため、AlON膜を厚く均一に成膜できる必要があることだ。2つ目は、トランジスタ構造が簡素なプレーナ型だけでなく、立体的なトランジスタ構造によって高い性能が得られるトレンチ型にも適用できるように、CVD(化学気相成長)法での成膜が目標になっている点だ。3つ目の課題になるのが、AlONのゲート絶縁膜中に電気的欠陥(電荷トラップなど)が存在しないようにするための工夫である。

共同研究チームは、これらの課題を解決すべく、量産装置を用いた研究開発を行った。具体的には、大阪大学が取り組んできたSiC-MOSFET向けのAlONゲート絶縁膜に関する知見を基に、東京エレクトロンとの共同研究によって、膜質を最適化したAlONゲート絶縁膜を、トレンチ型のトランジスタ構造上へCVD法によって均一に形成できる技術を開発した。さらに、このAlONゲート絶縁膜を用いたトレンチ型SiC-MOSFETを、ロームと京都大学が共同で試作し、デバイス性能と長期信頼性の向上を確認した。

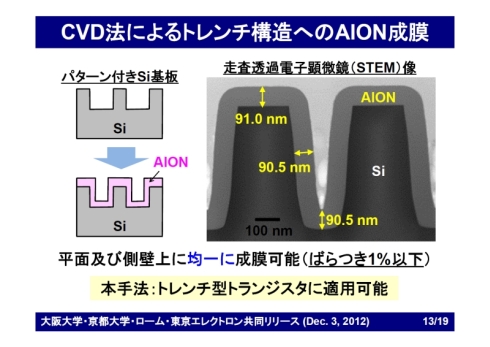

1つ目と2つ目の課題については、トレンチ型トランジスタ構造に用いられる凹凸のパターン付きSi基板を使ってAlONの成膜をCVD法で行い、凹凸の平面と側壁上に、ばらつき1%以下の膜厚でAlONを成膜できることを確認した。

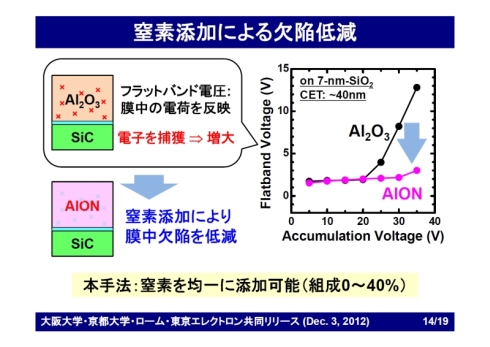

3つ目の課題であるAlONのゲート絶縁膜中における電気的欠陥の低減は、AlONのベース材料となる酸化アルミニウム(Al2O3)との比較によって確認した。AlON膜は、成膜した酸化アルミニウムの膜中に窒素を添加して形成する。この窒素添加によって、膜中の電気的欠陥を反映するフラットバンド電圧を大幅に抑制できることを確認できた。また、窒素の組成が40%までであれば、膜中への窒素の添加を均一に行える。

3つの課題を克服可能な技術を適用した量産装置を使って、AlONのゲート絶縁膜を用いたトレンチ型SiC-MOSFETを試作したところ、酸化シリコンを用いたものと比べて、絶縁破壊耐圧が1.5倍に向上し、リーク電流量も90%低減できた。

今回のAlONを成膜する技術は、ゲート絶縁膜とSiC基板の間に界面層を挿入した積層構造を持つゲート構造にも展開できる。これによって、素子構造設計の自由度を高められるので、SiC-MOSFETのさらなる低損失化、信頼性向上にもつなげられるという。

なお同技術は、米カリフォルニア州サンフランシスコで開催されている、半導体素子の国際学会「2010 IEEE International Electron Devices Meeting(IEDM 2012)」で発表される予定だ。

関連記事

次世代パワーデバイスの電動自動車応用の可能性

次世代パワーデバイスの電動自動車応用の可能性

現在使われているシリコン(Si)パワー半導体デバイスは、デバイス構造の工夫や独自のプロセス技術の開発により目覚しい進歩を遂げてきたが、その性能改善は限界に近づいてきている。次世代材料としては、炭化ケイ素(SiC)、窒化ガリウム(GaN)、ダイヤモンドなどのワイドバンドギャップ半導体が注目されてきているが、中でもSiCはウェーハ高品質化、大口径化と、製造プロセス技術の進展により、実用化がにわかに現実味を帯びてきた。 デンソーなど3社が6インチSiCウェーハを開発、EVなどの大容量インバータに最適

デンソーなど3社が6インチSiCウェーハを開発、EVなどの大容量インバータに最適

デンソー、昭和電工、豊田中央研究所の3社は、欠陥数を従来比で10分の1に削減した6インチSiCウェーハの開発を進めている。欠陥数の削減により、電気自動車(EV)などの大容量インバータに適した、電流容量の大きいSiCデバイスを歩留まり良く製造できるのが特徴だ。 安川電機がフルSiCドライブシステムを開発、インバータ部の出力密度は128kW/l

安川電機がフルSiCドライブシステムを開発、インバータ部の出力密度は128kW/l

安川電機は、SiC(シリコンカーバイド)デバイスを全面的に採用した次世代モータードライブシステムを開発した。Si(シリコン)デバイスを用いる同出力の従来品と比べて、システム全体の容積を25分の1に小型化したという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増