新時代到来! ヘテロジニアス・コンピューティング最新動向【後編】:プロセッサ/マイコン(1/3 ページ)

AMD Aシリーズプロセッサ“Kaveri”が正式に発表された。ヘテロジニアス・コンピューティングに向けたフレームワーク「HSA」対応アプリケーションの開発プラットフォームとしても期待を集めているKaveri。Kaveriの詳細やARMの動向を交えながらHSAの現状と今後を考察する。

HSA対応APU“Kaveri”

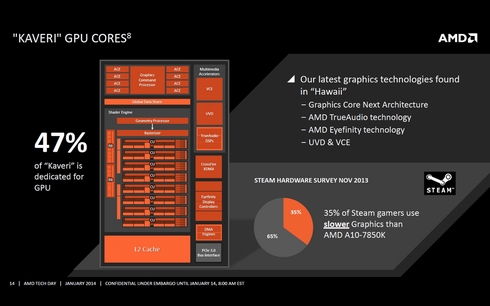

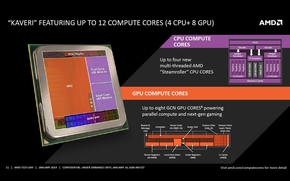

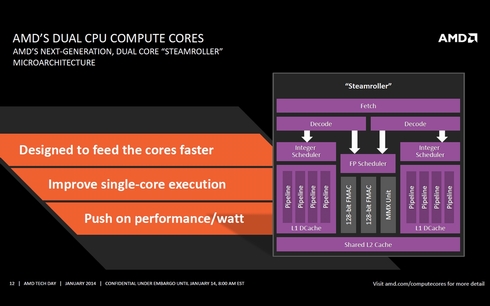

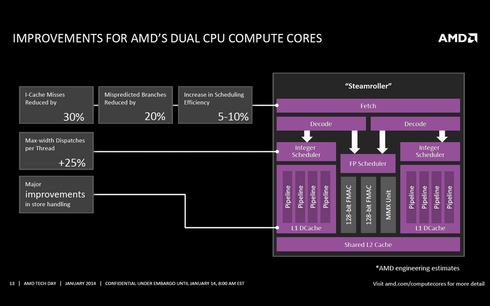

初のHSA対応APUとなった“Kaveri”は、CPUコアに第3世代のBulldozerアーキテクチャ“Steamroller”(スチームローラー)モジュールを採用するとともに、GPUコアを最新グラフィックスカードであるAMD Radeon R9 290Xと同等のGCN(Graphics Core Next)アーキテクチャに変更された。さらに、hUMAに対応すべく、CPUとGPUの内部バスも見直されている。

GPUをGCNアーキテクチャベースに変更

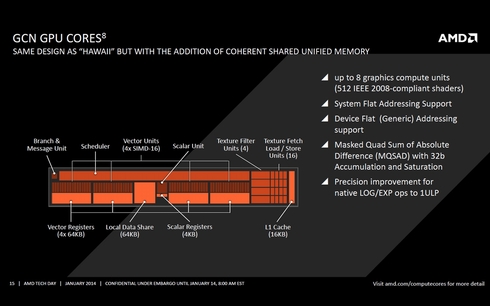

HSA対応での最大の進化は、GPUをGCNアーキテクチャベースに変更したことだ。GCNアーキテクチャでは、16個のベクター演算ユニット(ALU)でSIMDユニットを組み、このベクターSIMDユニットを4基(計64SP:Streaming Processor、またはRadeon Core)と1基のスカラプロセッサ、4基のテクスチャフィルタリングユニット、16KバイトのL1キャッシュで構成されるCU(Compute Unit)を最小単位としている。GCNアーキテクチャでは、このCUごとに命令発効ユニットやロード/ストアユニット、16Kバイトの命令キャッシュと32Kバイトのデータキャッシュが搭載され、個々のCUで独立したカーネル処理を可能にする。また、CUに搭載されたスカラユニットは、フル機能の整数演算機能を備え、コントロールフローやAMD GPUの演算実行単位である「Wavefront」(64スレッドをまとめたもの)の制御を行うことでSIMDユニットを効率よく機能させることができる。

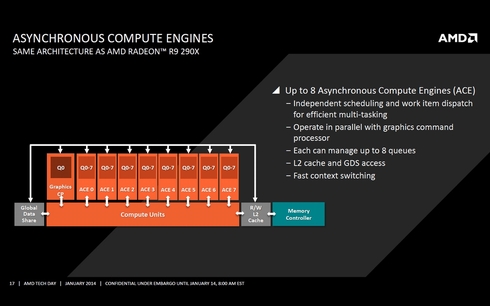

GCNアーキテクチャでは、汎用並列演算処理のフロントエンドプロセッサとしてACE(Asynchronous Compute Engine)を搭載し、同ユニットが演算のためのスケジューリングや命令発行を制御する。Kaveriでは、最大8基のCUでGPUを構成し、それと同数のACEを搭載し、CUの汎用コンピューティング処理を効率よく利用できるようにしている。このACE 8基という構成は、同社のフラグシップGPUである、44基のCUを統合するRadeon R9 290Xと同じ数であり、KaveriがいかにGPUを使った汎用GPU演算に注力した設計をしているかが分かる。

CUに汎用並列処理命令の発効などを行うACE(Acynchronous Compute Engine)は8基搭載されている。この数は、同社のフラグシップGPUであるRadeon R9 290Xと同じ数だ (クリックで拡大)

CUに汎用並列処理命令の発効などを行うACE(Acynchronous Compute Engine)は8基搭載されている。この数は、同社のフラグシップGPUであるRadeon R9 290Xと同じ数だ (クリックで拡大)もう1本の専用バス

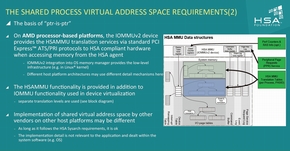

一方、内部バスの拡張では、CPUとGPUのメモリコヒーレンシを取るための専用バスを拡張している。従来のAMD-AシリーズAPU(Trinity/Richland)では、I/OコントローラとしてIOMMU v2(Input/Output Memory Management Unit)が搭載され、GPUがCPU側のメモリに仮想メモリアドレスでアクセスできるようにし、CPUとGPU間を256ビットの内部バス“Fusion Control Link(FCL)”で接続している。

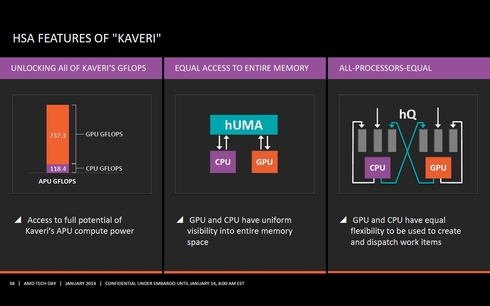

さらに、GPUとメモリコントローラを直接結び、より広帯域でのメモリアクセスを可能にする256ビット×2構成“Radeon Memory Bus”も用意することで、グラフィックス処理効率を引き上げている。これに対して、Kaveriでは、GPUとCPU間にさらにもう1本の256ビットバスが加えられている。これは、CPUとGPUのメモリコヒーレンシを取るための専用バス(コヒーレントバス)であり、CPUもしくはGPUがメモリを書き換えると、もう一方が書き換えられたメモリデータにアクセスできるようしている。ただし、CPUとGPU間でメモリコヒーレンシを取る必要がある場合は、お互いのメモリの同期に余分な時間を割く必要が生じる。このため、Kaveriでは従来のFCLはそのままに、もう1本の専用バスを加えることで、CPUとGPUがシームレスにメモリアドレス空間を共有できるようにしている。これこそが、HSAにおけるhUMAやhQに対応するためのハードウェア拡張といえる。

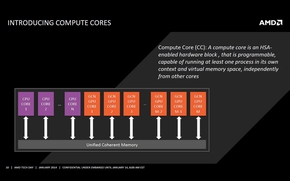

これらの拡張により、KaveriではCPUが持つ119GFLOPSに、GPUの737GFLOPSを加えた、856GFLOPSという強力な演算性能を、一般アプリケーションにも利用しやすくなる。このため、AMDはKaveriに搭載されたCPUコアとGPU(CU)を“Compute Core”と称し、4つのx86 CPUコアと8基のCUを合計し、「12 Compute Core APU」をうたっている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Kaveriのアーキテクチャを説明するAMD CTOのジョー・マクリ氏

Kaveriのアーキテクチャを説明するAMD CTOのジョー・マクリ氏