ASICからFPGA/All Programmable SoCへ、Cベースに進化する開発環境:X-fest 2015 技術セミナーリポート(1/3 ページ)

アヴネット主催の技術セミナー「X-fest 2015」の基調講演に、ザイリンクスの査 錚(サ シン)氏が登壇した。FPGA・SoCにおけるハードウェアの性能向上と拡張性に加えて、Cベース言語を中心とした開発環境への対応などについても触れた。

2015年1月30日、東京都内でアヴネット主催の技術セミナー「X-fest 2015」が開かれた。テーマは「最新のFPGA・SoCを使いこなす」である。本稿ではザイリンクスでマーケティング部/プロダクトマーケティングスペシャリストを務める査 錚(サ シン)氏による基調講演について、その概要を紹介する。

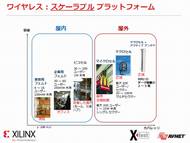

基調講演のテーマは「スマートとスケーラビリティの将来」。査氏はまず、アプリケーションによってスケーラビリティへの対応が異なる点を指摘。特に「モノづくり」におけるスケーラビリティは、「プラットフォームを集約してスケーラビリティを実現して行くことが重要」と述べ、その一例を紹介した。

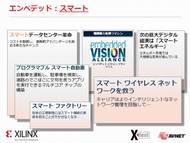

例えば無線通信においては、取り扱うデータ容量とカバーする範囲によって、システムを拡張していく必要がある。有線通信では、ネットワーク制御をソフトウェアで実現する手法「Software Defined Networking(SDN)」を用いることで、システム拡張時にも動作を停止させる必要がなくなる。つまり、「システムの特性に合わせた運用と拡張が重要だ」と語る。組込み機器に関してはさらなる「スマート」機能が要求されるとみている。スマートフォンが数年前のPCを超える性能や機能を備えるようになった。「この次は自動運転に向かう自動車向けに、より高度化されたスマート機能が要求されることになるだろう」と話す。

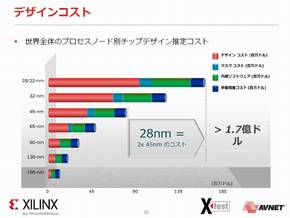

続いて、ネットワークにおけるIPトラフィック量の急増とICチップの進化について紹介した。IPトラフィック量は2011年に比べて、2015年には約3倍に増加するという予測もある。このことは、ICチップに膨大なデータを高速に処理できる性能が要求されることになる。査氏は「ザイリンクス製FPGAにおいても、40nmプロセスで製造される製品以降は、通信の帯域幅も急激に広がった」と語る。一方でICチップの開発/設計コストは高騰し、売上高に占めるR&Dコストの比率を押し上げる結果になっている。同社の試算によれば、28nmプロセスノードを使ったIC設計コスト(マスク設計やソフトウェア開発などのコスト含む)は、45nmプロセスノード製品に比べて、約2倍に上昇するという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Musk氏は「半導体製造の再定義」を目指すのか

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- 世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

ザイリンクスでマーケティング部/プロダクトマーケティングスペシャリストを務める査錚氏

ザイリンクスでマーケティング部/プロダクトマーケティングスペシャリストを務める査錚氏