ARMから見た7nm CMOS時代のCPU設計(4):福田昭のデバイス通信(15)(1/2 ページ)

今回は、ロジック設計の変遷をたどっていこう。現在の主流である「スタンダード方式」の他、FPGAに代表される「セミカスタム」などがある。

【ARMから見た7nm CMOS時代のCPU設計:バックナンバーはこちら】

ロジック設計の変遷

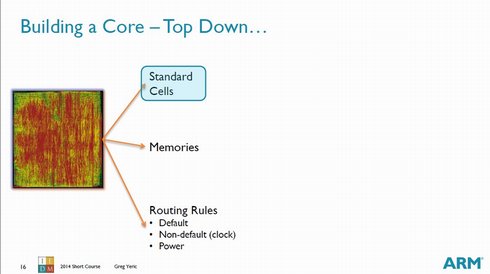

シリコンダイを構成する回路ブロック(「コア」、「マクロ」、「IP」などと呼称される)を大別すると、ロジック、メモリ、その他に分かれる。ここでその他とは、クロック配線や電源配線などのブロックを意味する。

CPU設計は基本的にはロジック設計である。ロジック設計の主流は、「スタンダードセル」と呼ぶ、規格化された論理セルを使った設計方式である。これを「スタンダードセル方式のLSI設計」とも呼称する。わざわざこのように呼ぶのは、当然ながら、他の設計方式があるからだ。1つは「フルカスタム方式」で、トランジスタを1個ずつ、シリコン上で設計する。トランジスタの形状を最適化できるので、シリコン面積は最も小さく、性能は最も高くなる。

余談になるが、40年ほど以前の1970年代には、ロジック設計といえば「全て」このフルカスタム方式を意味した。しかしフルカスタム方式はいわば手作りであり、トランジスタの数が増えると、設計工数が幾何級数的に増えてしまうという大きな問題を抱えていた。これは設計者を大幅に増やすか、あるいは設計期間を大幅に延ばすことを意味する。いずれも実用的には受け入れられない。

半導体が搭載するトランジスタ数が増えたことでフルカスタム方式がほぼ破綻したのが、1980年代である。そこで登場したのが当時、「セミカスタム」と呼ばれた設計手法である。セミカスタムの設計手法は2種類あり、1つが「スタンダードセル方式」、もう1つが「ゲートアレイ方式」と呼ばれた。

1980年代にセミカスタム設計に普及したのは、ゲートアレイ方式である。ゲートアレイ方式のLSI設計では、規格化された論理セルのアレイがあらかじめシリコンに作りこまれた状態で、設計を始める。すなわち設計作業とは、粗く言ってしまうと「配線(ルーティング)」工程だけになる。このため、設計期間が非常に短くて済む。また配線工程を残した「マスタースライス」と呼ばれるシリコンから製造工程が始まるので、設計完了から製造完了までの期間が、フルカスタム方式やスタンダードセル方式に比べると、はるかに短いという長所もあった。

ただしゲートアレイには弱点もある。使用しない論理セルが存在することである。言い換えると、シリコンダイ面積が大きくなってしまう。開発期間を短くする代わりに、シリコンダイ当たりの製造コストはやや高価になる。多品種少量生産に向いた設計手法だといえる。

現在では、ゲートアレイはあまり使われていない。代わりにセミカスタムLSIの主流となったのはFPGAだ。FPGAは、SRAMをベースとした書き換え可能な論理セルを備えたシリコンダイである。あらかじめFPGA専用のツールで開発した設計データによって、FPGAのダイに回路を書き込む。設計完了から製造完了までの期間はほぼゼロに等しいので、納期はゲートアレイよりもはるかに短い。そして設計ミス(バグ)が見つかっても、設計データを書き直してFPGAに上書きするだけで済む。ゲートアレイに比べると、すごく使い勝手が良い。

FPGAは1980年代に登場した当初は、ゲートアレイに比べるとシリコンの単価(論理ゲート当たりの単価)が高価だった。このため、試作評価や極少量生産といった限定的な利用にとどまっていた。しかしFPGAベンダーが微細化を積極的に推し進めたことによって、シリコン面積が小さくなり、論理ゲート当たりの単価は急速に低下した。現在では、セミカスタムLSIの大半はFPGAとなっている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増