EE Times Japan >

プロセス技術 >

ARMから見た7nm CMOS時代のCPU設計(4):福田昭のデバイス通信(15)(2/2 ページ)

» 2015年03月25日 12時00分 公開

[福田昭,EE Times Japan]

CPU設計の主役はスタンダードセル

FPGAのシリコンダイ面積が小さくなったとは言っても、不要な論理セルをゼロにすることはできない。シリコン面積の小ささでは、スタンダードセル方式にはとてもかなわない。このため、CPU設計の主流は現在でも、スタンダードセル方式である。当然ながら、ARMのCPUコア設計も、スタンダードセル方式を採用している。

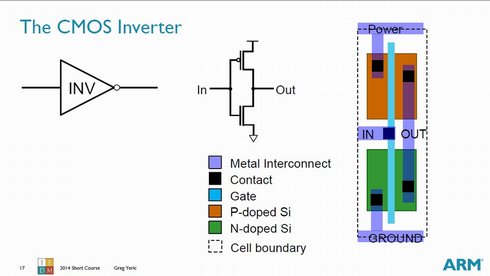

ARMの設計技術者は講演で、代表的な論理ゲートをスタンダードセル方式で具体化したレイアウトのスライドを示した。1つは、CMOSインバータである。スライドでは、左にインバータの論理記号(NOT)、中央にトランジスタ回路、右にシリコンのレイアウトを示した。トランジスタ回路は上から電源配線、pチャンネルMOSトランジスタ、入力端子と出力端子、nチャンネルMOSトランジスタ、そして最下部の接地配線となっている。これを右のレイアウトと比べると、上から下までの関係が、非常に良く似ていることが分かる。レイアウトでも上端に電源配線があり、その下にpMOSトランジスタがあり、中央部に入力端子と出力端子、その下にnチャンネルMOSトランジスタ、下端が接地配線となっている。

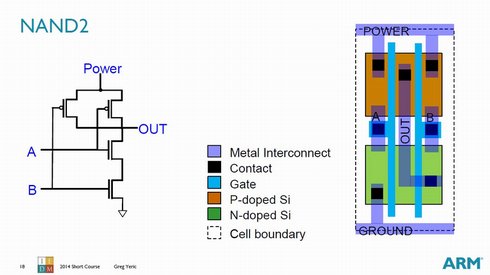

もう1つのスライドは、2入力NANDゲートである。左にトランジスタ回路、右にシリコンのレイアウトを示していた。この場合も、トランジスタ回路とレイアウトがよく似ていることが分かる。上端に電源配線があり、中央の入力端子と出力端子を挟んで上部が2個のpMOSトランジスタ、下部が2個のnMOSトランジスタという配置になっている。下端は接地配線である。

(次回に続く)

関連記事

FPGAの進化を上回れ! 生産5年目に突如現れた起動不良

FPGAの進化を上回れ! 生産5年目に突如現れた起動不良

FPGAはハードウェアをプログラムできるデバイスで機器の高性能化や小型化には欠かせなくなってきている。複数のFPGAが実装される基板も多くなった。今回は、重要部品となったFPGAに起因したと思われるトラブルと、その原因について詳しく調査を行ったので紹介する。 「これは新概念の組み込みハード基盤」、ザイリンクスがARM集積FPGAの詳細を発表

「これは新概念の組み込みハード基盤」、ザイリンクスがARM集積FPGAの詳細を発表

ザイリンクスは2011年3月1日、アームのプロセッサコア「Cortex-A9 MPCore」をハードマクロとして集積するFPGA製品群「Zynq(ジンク)」を発表し、同製品群の第1弾となる4品種の詳細を明らかにした。 20nmプロセスFPGAの量産始まる

20nmプロセスFPGAの量産始まる

ザイリンクスは2014年12月、20nmプロセスを使用したFPGA「Kintex UltraScale KU040」の量産を開始したと発表した。 MAX 10 FPGAでマイコンの置き換えなどを提案――アルテラ

MAX 10 FPGAでマイコンの置き換えなどを提案――アルテラ

アルテラは、「組込み総合技術展/Embedded Technology 2014」(2014年11月19〜21日)で、「MAX 10 FPGA」を始め、FPGAや電源などに関する最新情報を7つのゾーンで紹介した。 もうかる通信機器はFPGAでこそ実現できる、国内メーカーの海外展開に期待

もうかる通信機器はFPGAでこそ実現できる、国内メーカーの海外展開に期待

大手FPGAベンダーであるXilinxは、最先端の半導体製造プロセスを用いた製品開発に意欲的なことで知られている。同社は、TSMCの20nmプロセスを用いた次世代品を、2013年10〜12月期にサンプル供給する方針を既に明らかにしている。日本法人のザイリンクスで社長を務めるサム・ローガン氏に、通信機器におけるASIC/ASSPからFPGAへの置き換えの進展や、競合のAlteraが発表したIntelの14nmプロセス採用に対する見解などについて聞いた。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR