ARMから見た7nm CMOS時代のCPU設計(16)〜次世代メモリへの期待:福田昭のデバイス通信(27)(1/2 ページ)

今回はSRAMの消費電力に視点を移す。CPUの電源電圧の低下に伴うSRAMビット不良や、待機時と動作時で大きく異なるSRAMの消費電力に焦点を当て、なぜ、次世代の不揮発性メモリ「スーパーメモリ」に期待がかかっているのかを説明しよう。

低電圧化で最初に発生するのがSRAMビット不良

前回は、CPUのオンチップキャッシュに使われている、SRAM技術のスケーリング問題を論じた。

CPUの電源電圧を下げていくと、最初に発生する不良は大抵、オンチップキャッシュ(SRAM)のビット不良になる。電源電圧の低下によってSRAMセルが記憶しているデータ(ビット)の値が不安定になり、データを読み出せなくなってしまう。あるいは、データをうまく書き込めなくなる。

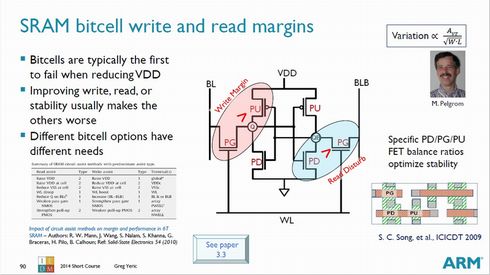

SRAMセルのデータ読み出しとデータ書き込みを安定化する手法は幾つか存在する。例えばトランジスタの大きさを制御する。6個のトランジスタで構成される標準的なSRAMセル(6トランジスタ・セル)では、ビット線対につながる2個のトランジスタ(PG)と、フリップフロップを構成する4個のトランジスタの中でプルアップ側の2個のトランジスタ(PU)と、プルダウン側の2個のトランジスタ(PD)に分けて考える。

読み出しを安定化する(読み出しマージンを増加させる)ためには、PGを小さくし、PUを大きくしたい。一方、書き込みを安定化する(書き込みマージンを増加させる)ためにはPGを大きくし、PUを小さくしたい。さらにはPDをPGよりも大きくすることで、読み出しディスターブを回避したい。こういった関係の中で、トランジスタの大きさを調節する必要がある。

待機時と動作時で大きく違うSRAMの電力消費事情

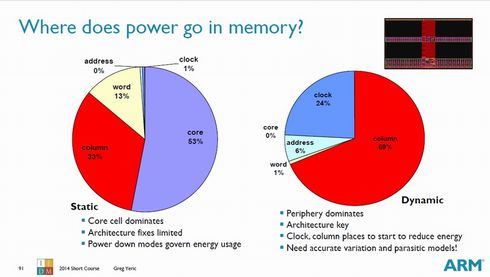

SRAMの消費電力に視点を移すと、待機時と動作時ではその様相がかなり違う。待機時消費電力の半分を占めるのは、メモリセルアレイ(コア)である。メモリセルのリーク電流を抑制することが、待機時消費電力の低減につながることが分かる。

これに対して動作時消費電力は、周辺回路によるものがほぼ全てである。コアによる消費電力は、無視して良いくらいに低い。周辺回路のカラム部(ビット線対とセンスアンプ列)が消費電力の約7割、クロック回路が消費電力の約4分の1を占める。両者の合計で動作時消費電力の9割を超える。

周辺回路のカラム部は、待機時でも消費電力の約3分の1を占める。全体の消費電力を低減することを考えたときには、カラム部の消費電力をいかに低減するかが重要なことが分かる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- 「Rapidusの隣」に光電融合パッケージ開発拠点、28年度の完成目指す

- ルネサス26年1Qは増収増益 車載/AI好調で「足元は当面強い」