ARMから見た7nm CMOS時代のCPU設計(16)〜次世代メモリへの期待:福田昭のデバイス通信(27)(2/2 ページ)

フラッシュメモリは低電力モバイルCPUに向かない

SRAMの待機時消費電力を低減する最も単純な方法は、電源電圧をオフにすることだ。もちろん、電源電圧をオフにする直前に、データを不揮発性メモリにコピーしておく必要がある。するといっそのこと、不揮発性メモリをキャッシュにしたくなる。

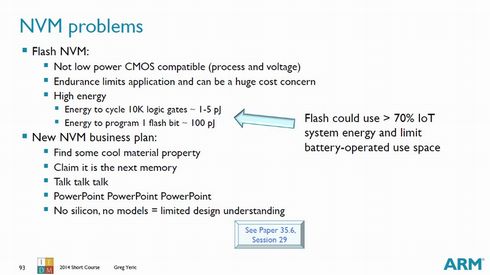

しかし不揮発性メモリの代表であるフラッシュメモリは、モバイルCPUのオンチップメモリには適していない。その大きな理由は、書き込みエネルギーが大きいことと、CMOSロジックとプロセスの互換性がないことである。フラッシュメモリはまた、書き換え回数に制限がある。このことは、応用範囲を限定する。

フラッシュメモリの書き込みエネルギーはロジックに比べると膨大で、1ビットのデータを書き込むためには100ピコジュール前後を必要とする。ところがCMOSロジックは、1万ゲートの消費エネルギーですら1サイクル当たりで5ピコジュール程度にすぎない。フラッシュメモリ1ビットの約20分の1以下である。

待たれる「スーパーメモリ」の登場

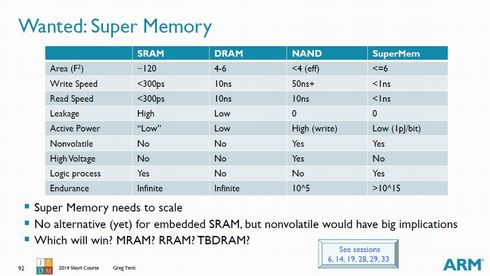

そこで期待がかかるのが、新しいタイプの不揮発性メモリである。この「スーパーメモリ(次世代不揮発性メモリ)」は、粗く言えばDRAMとNANDフラッシュメモリの「いいとこ取り」だ。メモリセル面積はDRAMなみに小さく、スケーリングが可能で、書き込み速度と読み出し速度はDRAMよりも高速で、ロジックとプロセスの互換性があり、電源をオフにしてもデータが残り、書き換え回数は無制限に近いことが望ましい。

このような「スーパーメモリ」が近い将来に実現するかどうかは分からないものの、候補は存在する。磁気メモリ(MRAM)技術や抵抗変化メモリ(RRAM)技術などである。これらのメモリ技術の進展に期待したい。

(次回に続く)

- AI/HPCシステムの死命を制する消費電力・放熱設計(前編)

- AI/HPCシステムのメモリ/ストレージ階層とHBMの高性能化

- ミニダイ(チップレット)間接続におけるSTCO

- 先進パッケージのシステム・製造協調最適化(STCO)

- インターポーザに複数のシリコンダイを近接して並べる2.5次元集積化

- 複数のミニダイ(チップレット)を1つのパッケージに収容する

- モノリシック集積の限界を超えるヘテロジニアス集積化

- AIサーバの高性能化に不可欠となった先進パッケージング技術

- 創刊前の20年間(1985年〜2005年)で最も驚いたこと:「高輝度青色発光ダイオード」(後編)

- 創刊前の20年間(1985年〜2005年)で最も驚いたこと:「高輝度青色発光ダイオード」(前編)

関連記事

“次世代メモリ”の域を出ないFRAM、量産規模を上げて低価格化を

“次世代メモリ”の域を出ないFRAM、量産規模を上げて低価格化を

SRAMやDRAM、EEPROMを置き換えるとして大いに期待されていたFRAMは、量産こそ始っているものの、完全に普及しているとはいえず、いまだに“次世代メモリ”の域を出ない。だが、一定のニーズはある。 量子メモリ不要の長距離量子通信を可能にする量子中継手法を確立

量子メモリ不要の長距離量子通信を可能にする量子中継手法を確立

NTTとトロント大学は2015年4月15日、通信距離100kmを超えるような長距離量子通信に必要な量子中継を、物質量子メモリを使用せずに、光の送受信装置だけで実現できる「全光量子中継方式」を理論的に確立したと発表した。 次世代メモリ市場、2020年には70億米ドル規模に

次世代メモリ市場、2020年には70億米ドル規模に

ReRAMやMRAMといった不揮発RAM市場は、今後急成長を遂げ、2020年には70億米ドル規模に拡大すると見られている。NAND型フラッシュメモリやDRAMに取って代わるには、微細化とビット当たりの価格が鍵になりそうだ。 NANDフラッシュ、売価下落も市場規模は拡大――2014年10〜12月

NANDフラッシュ、売価下落も市場規模は拡大――2014年10〜12月

DRAMeXchangeによると、2014年第四半期におけるNAND型フラッシュメモリの世界市場は、全体として好調だったようだ。ただし、価格の下落は続いている。今後、Samsung Electronics(サムスン電子)は3次元NANDフラッシュ、東芝は15nmプロセスへの移行を加速させると見られている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- イラン戦争の長期化が半導体業界に及ぼす深刻な影響

- 東芝との協議やデンソー提案への対応、ロームが新声明

- NVIDIA製GPU搭載サーバのコスト/スペックを分析してみた

- ロームとデンソー、東芝、三菱電機……国内パワー半導体再編の行方

- IBMとLamが「サブ1nmチップ」で協業 高NA EUV導入加速へ

- AIの競争軸は半導体から電力へ――日本の戦略の「死角」に

- 「これまでにないダイナミックレンジ」 ソニーのLOFIC画素4Kセンサー

- Micron、PSMCの300mm工場買収完了 第2工場も建設へ

- 全固体二次電池の「200℃動作」を実演、日本電気硝子

- 「世界初」酸化ガリウムをSi基板にエピ成長、名大ら