16nm世代「Zynq」のテープアウトを発表:FPGA ザイリンクス

Xilinxは2015年7月6日、16nmプロセスを用いたCPUコア搭載型FPGA「All Programmable Zynq UltraScale+ MPSoC」をテープアウトしたと発表した。

16nm世代で最初

Xilinx(ザイリンクス)は2015年7月6日、16nmプロセスを用いたCPUコア搭載型FPGA「All Programmable Zynq UltraScale+ MPSoC」(以下、Zynq UltraScale+)をテープアウトしたと発表した。同社16nm世代FPGAのテープアウトの発表は今回が初めて。

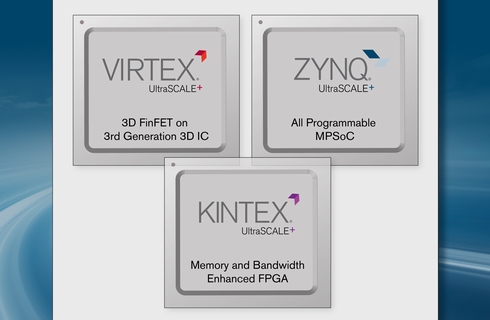

同社は、TSMCの16nm FinFET プラス(FF+)プロセスを用い、16nm世代FPGA「UltraScale+ ファミリ」を製造し、2015年末より出荷する計画。UltraScale+ ファミリとしては、ハイエンドFPGA「Virtex UltraScale+」、ミドルエンドFPGA「Kintex UltraScale+」、CPUコア搭載型FPGA「Zynq UltraScale+」の3ファミリを展開する予定になっている。

今回、テープアウトを発表したのは、Zynq UltraScale+ファミリ。CPUコア「ARM Cortex-A53」を4個、「同 Cortex-R5」を2個搭載するFPGA。他に、GPUコアとして「ARM Mali-430」を備え、ペリフェラルホスト機能、パワーマネージメント機能を内蔵。画像検査装置や自動車の先進運転支援システム(ADAS)などの用途を見込んでいる。

16nm世代、2015年中に出荷へ

Xilinxでは、2015年10-12月中に、16nm世代FPGAであるUltraScale+ファミリの最初の出荷を開始するとしている。

関連記事

16nm世代FPGA、ザイリンクスが「UltraScale+」ファミリを発表

16nm世代FPGA、ザイリンクスが「UltraScale+」ファミリを発表

ザイリンクスは、16nmプロセス技術を用いた次世代FPGA「UltraScale+」ファミリを発表した。従来の28nmプロセスFPGA/SoCに比べて、消費電力当たり2〜5倍のシステム性能を実現することが可能となる。 5年連続で国内売り上げ記録を更新! 「国内でも競合を超えた」

5年連続で国内売り上げ記録を更新! 「国内でも競合を超えた」

FPGA大手ベンダーのXilinxの日本法人は、2015年3月期に5年連続となる売上高最高記録を更新したという。日本法人社長のサム・ローガン氏に好調の要因などを聞いた。 IntelのAltera買収は成功するのか――Xilinxの存在感が増す可能性も

IntelのAltera買収は成功するのか――Xilinxの存在感が増す可能性も

Intelにとって過去最大規模となったAlteraの買収。x86プロセッサとFPGAを統合することで、新しい製品の開発や、これまでにない分野を狙える可能性はある。Alteraにとっては、Xilinxからシェアを奪うきっかけになるかもしれない。一方で、今後AlteraとのビジネスにIntelが絡んでくることに不安を抱く既存顧客が、Xilinxを頼るようになるのではないかと見るアナリストもいる。 ザイリンクス優位は、20nm/16nm世代でも揺るがない

ザイリンクス優位は、20nm/16nm世代でも揺るがない

ザイリンクス日本法人は、現行の主力28nmプロセス採用FPGAの受注が好調だという。同社社長を務めるサム・ローガン氏に好調の理由や、今後、投入を本格化させる20nmプロセス採用FPGA製品のビジネス展望などを聞いた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ソニーセミコンとTSMCが合弁会社設立を検討

- 半導体検査装置向けレンズの研磨工程が稼働、生産能力2.6倍に

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

16nm世代FPGA「UltraScale+ファミリ」 出典:Xilinx

16nm世代FPGA「UltraScale+ファミリ」 出典:Xilinx