EE Times Japan >

先端技術 >

Rapidus、千歳で製造した2nm GAAトランジスタの試作品を初展示:SEMICON Japan 2025(1/2 ページ)

Rapidusは「SEMICON Japan 2025」(2025年12月17〜19日)に出展し、北海道千歳市の開発/製造拠点「IIM(イーム)」で製造した2nm GAA(Gate All Around)トランジスタや600mm角 再配線層(RDL)インターポーザーパネルの試作品を展示した。

» 2025年12月24日 10時30分 公開

[浅井涼,EE Times Japan]

Rapidusは「SEMICON Japan 2025」(2025年12月17〜19日)に出展し、北海道千歳市の開発/製造拠点「IIM(イーム)」で製造した2nm GAA(Gate All Around)トランジスタや600mm角 再配線層(RDL)インターポーザーパネルの試作品を展示した。

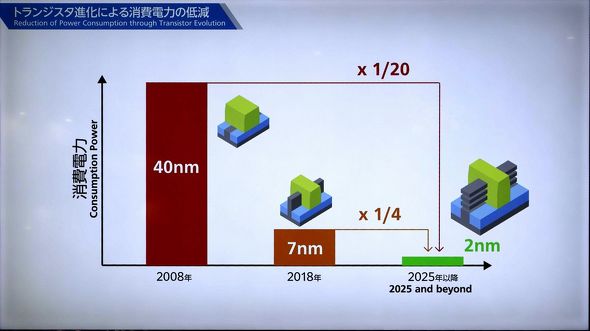

2nm GAAトランジスタの消費電力は7nm FinFETの4分の1

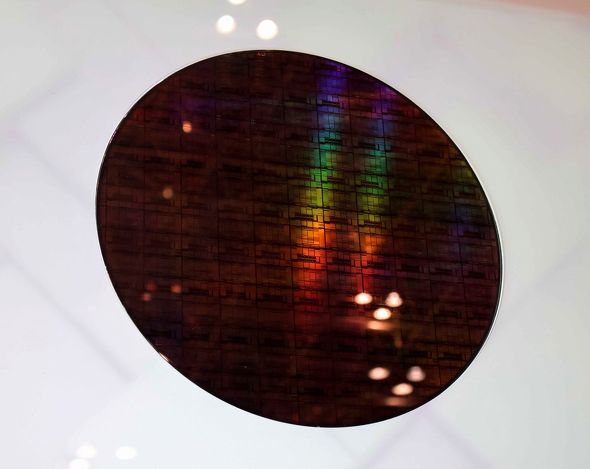

Rapidusは2025年6月16日、北海道千歳市に構える開発/製造拠点「IIM(イーム)」の前工程パイロットラインに初めてウエハーを投入。同月28日には最初の2nm GAAトランジスタの試作品が完成し、動作を確認した。IIMで製造した試作品の実物を展示会などで展示するのは初めてだといい、ブースには人だかりができていた。

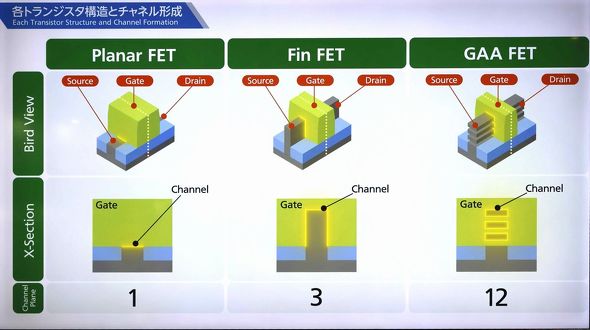

ブースでは試作品の実物展示に加えて、ディスプレイで2nmプロセスやGAA構造の利点の解説も行った。2008年ごろの最先端プロセスだった40nmのプレーナー型トランジスタと比べると、2nm GAAトランジスタは消費電力を約20分の1まで削減できる。2018年ごろの最先端プロセスだった7nmのFinFETと比べても約4分の1だ。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ソニーセミコンとTSMCが合弁会社設立を検討

- 半導体検査装置向けレンズの研磨工程が稼働、生産能力2.6倍に

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

Special SitePR

あなたにおすすめの記事PR