14/16nm世代のSRAMと第3の2Dデバイス材料:福田昭のデバイス通信 IEDM 2015プレビュー(5)(2/3 ページ)

» 2015年11月11日 09時30分 公開

[福田昭,EE Times Japan]

先端SRAMの劣化特性がレイアウトで変化

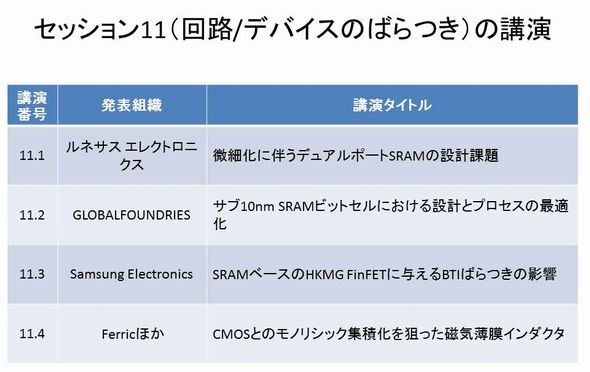

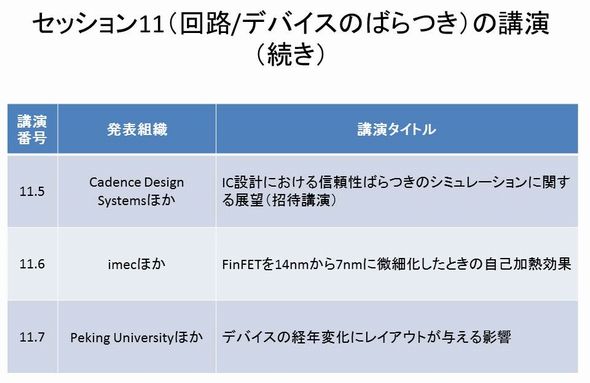

セッション11(回路とデバイスの相互作用)のテーマは「CMOSの微細化と回路/デバイスのばらつき」である。このセッションでは、SRAMの微細化に伴う課題を扱う講演が相次ぐ。

ルネサス エレクトロニクスは8トランジスタのSRAMセル構造を微細なデュアルポートSRAM向けに検討した結果を報告する(講演番号11.1)。16nmのFinFET技術によってデュアルリードライト(2RW)のデュアルポート256KビットSRAMマクロを設計し、試作した。電源電圧0.5V、最小信号電圧120mVで動作を確認している。韓国のSamsung Electronicsは、BTI(Bias Temperature Instability)のばらつきが微細な大容量SRAMに与える影響を検討した(講演番号11.3)。具体的には、14nmのFinFET技術で128MビットのSRAMでトランジスタとメモリセル、回路性能に与える影響を調べた。

SRAM以外では、長期信頼性のレイアウト依存性を見いだした研究成果が目立つ。中国のPeking Universityと米国のThe University of Texas at Austin、中国のSemiconductor Manufacturing International Corporation(SMIC)による共同研究の成果である(講演番号11.7)。BTIによる劣化とホットキャリア注入(HCI)による劣化でレイアウトによる違いが生じた。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

- デンソー、ロームに対する株式取得提案を正式表明

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- イラン戦争の長期化が半導体業界に及ぼす深刻な影響

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- 東芝との協議やデンソー提案への対応、ロームが新声明

- 高NA EUVを「産業規模へ拡張」、imecがEXE:5200導入

Special SitePR

あなたにおすすめの記事PR