300GHz帯で32値のQAM信号を出力するミリ波送信器:福田昭のデバイス通信 ISSCC 2016プレビュー(7)(1/2 ページ)

今回はセッション19〜21までを紹介する。セッション20では、パナソニックが発表する、300GHz帯で32値のQAM信号を出力する送信器チップに注目したい。チャンネル当たりのデータ送信速度は17.5Gビット/秒で、6チャンネルの5GHz帯域出力を備えている。

ロック時間が1.2マイクロ秒の高速デジタルPLL

前回に続き、ISSCC 2016の技術講演プレビューをお届けする。技術講演の最終日である、2016年2月3日(水曜日)午前に発表予定の講演論文のハイライトである。

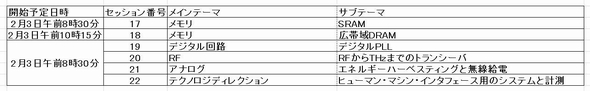

この時間帯は、セッション17からセッション22までの6本のセッションが予定されている。セッション17とセッション18は同じ会議室を使用したハーフセッションで、午前の前半がセッション17、午前の後半がセッション18というスケジュールである。残りのセッション19〜セッション22は、別々の会議室で同時に進行する。

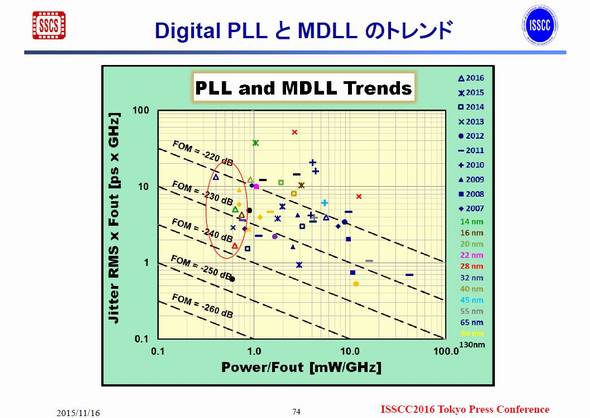

セッション19のメインテーマは「デジタル回路」、サブテーマは「デジタルPLL」である。このセッションでは、デジタルPLLに関する2件の講演が興味深い。

Broadcomは、モバイルSoC(System on a Chip)の動的周波数スケーリングや動的コアカウント・スケーリングなどに向けた高速デジタルPLLを提案する(講演番号19.1)。0.5GHzから9.5GHzの範囲で、ロック時間は1.2マイクロ秒と短い。ジッタは±1.25%UIにとどまる。製造技術は16nmのCMOS。

東芝は、ドライバレスのオールデジタルPLLに向けた要素技術である、高性能TDC(Time to Digital Converter)を発表する(講演番号19.7)。シングルスロープ型A-D変換回路を採用し、1.6ピコ秒(0.27LSB)の積分非直線性誤差(INL)と、8.9ピコ秒(5.5ビット)の有効ビット数(ENOB)を得た。消費電力は360μWと低い。製造技術は65nmのCMOS。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増