Intel、「ムーアの法則は微細化の実現ではない」:10nm以降もCMOSに注力(2/3 ページ)

SRAMの微細化

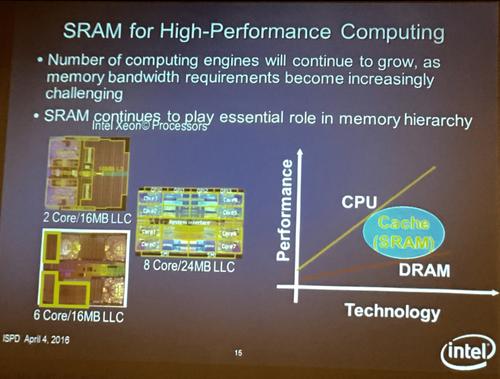

Zhang氏は、最初の例として、SRAMを取り上げた。SRAMは近年、マルチコアプロセッサ用オンチップキャッシュとして使用できるために重要性が高まっているが(DRAMがマルチコアプロセッサの進化に対応できていないため)、そのアーキテクチャは6世代前から変化していない。

同氏は、「プロセッサの設計では、DRAMの性能がプロセッサに追い付いていないため、より大きなSRAMキャッシュが必要になっている。SRAMが抱える課題を解決するには3次元化で対応が可能だが、最良の方法は、プレーナ(平面)型のオンチップSRAMの面積の低減と性能を向上させることだ」と述べている。

SRAMは、これまでわずかに改良されたものの、過去20年もの間、基本的にあまり変化していない。しかしIntelは、14nmプロセス以降への進展を見据え、SRAMセルのさらなる微細化の実現を目指し、設計開発に取り組んできた。

SRAMの微細化において大きな問題は、読み出し/書き込み条件の不整合が増大するという点だ。Zhang氏は、「読み出し時の回路へのディスターバンスを最小化することによって、SRAMの読み出し時間を容易に高速化できる。一方で、書き込み時の回路へのディスターバンスを最大化することで、書き込み性能を高めることが可能になる。ただし、両方を同時に実行することは不可能だ」と述べる。

同氏は、「ここ数年間は、微細化というよりは、新しいトランジスタアーキテクチャと新材料の開発が進んでいる。例として、高誘電率膜/金属ゲート(High-k/Metal Gate)技術や、3次元FinFETのトランジスタアーキテクチャなどが挙げられる」と続けた。

さらに同氏は、「例えばSRAMの場合、電源電圧をドアノブのように回して、読み出し/書き込みの両方の最良ポイントを得られるような、新しいアーキテクチャが開発されている」と説明する。

特にオンチップ回路の場合は、書き込みカラムには低電圧を供給し、読み出しカラムへの供給電圧を増加させるといったように、読み出し/書き込み時の供給電圧を変えることで、不良/ディスターバンスを緩和できる“妥協点”を見つけ、SRAMセルの性能の全体的な向上を実現するという。

SRAM向けのダイナミックスリープモードでは、動作時のSRAMアレイへの電力も調整できるため、常時指定されたSRAMセルに対してのみ低電圧または高電圧を供給しながら、アレイ全体の99%をスリープモードで維持することが可能だという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

- デンソー、ロームに対する株式取得提案を正式表明

- イラン戦争の長期化が半導体業界に及ぼす深刻な影響

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- 東芝との協議やデンソー提案への対応、ロームが新声明

- 高NA EUVを「産業規模へ拡張」、imecがEXE:5200導入

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- キオクシアが超高IOPS SSD開発 NVIDIA Storage-Nextに対応

- AIの競争軸は半導体から電力へ――日本の戦略の「死角」に

DRAM技術はプロセッサの性能に追い付いていない

DRAM技術はプロセッサの性能に追い付いていない