Intel、「ムーアの法則は微細化の実現ではない」:10nm以降もCMOSに注力(3/3 ページ)

アナログ周辺回路のデジタル化

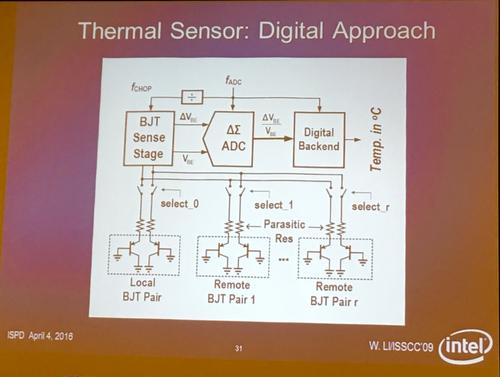

Intelはこれまで、自社プロセッサのアナログ機能のデジタル化にも取り組んできた。アナログ回路では、デジタル回路のように微細化によるメリットは享受しにくいためだ。例えば、電力を最小化するための電圧スケーリングや、熱暴走を防止するための温度検出回路などを、デジタル回路に変換したという。

また、アナログ電圧制御発振器(VCO)をデジタル電圧制御発振器(DCO)に、アナログトランジスタを熱暴走検出用BJT(バイポーラ接合トランジスタ)に変えるなど、プロセッサ周波数に対応した一般的なアナログPLL(Phase Locked Loop)に搭載された全てのアナログ機能を変更している。

Intelの技術者たちが完全なデジタル化の方法を見つけることができない回路については、ハイブリッド型ミックスドシグナルの“デジタルアシスタント技術”を適用することにより、デューティサイクルを最適化しているという。例えば、14nmプロセスを適用した最新のプロセッサに搭載された回路では、入力/出力速度を40Gビット/秒(GHz)に高めることに成功した。

将来的には適応設計の実現へ

Zhang氏によると、継続的な微細化の実現は、適応型の電力管理と電圧スケーリングを実現できるかどうかにかかっているという。特にスリープモード時は、電圧スケーリングを下げることによって電力を管理することが不可欠だが、SRAMの動作を維持するための十分な電圧も必要だ。

次世代トランジスタは、固定バイアスではなく可変バイアスを採用し、各チップのトランジスタの特性に応じた適応型の制御バイアスによって動的に調整されるようになるだろう。

現在では、受動制御によってトランジスタにバイアス電圧をかける場合、多くのダイが無駄に使われてバス歩留りが低下する。しかし、適応型のバイアス制御では、不良ダイのバイアスレベルを動的に制御して最適化することにより、通常と同程度またはそれ以上の優れた性能を実現できるという。

Zhang氏は、上述した適応技術で性能の向上を図ったCMOSコアが、10nmプロセス以降も主流であると確信しているという。一方で、GaN(窒化ガリウム)や磁性材料、III-V族化合物半導体、量子ビット(Qubit)など新しい材料が、CMOSコアをサポートする周辺回路において主要な役割を果たすようになるとした。

【翻訳:田中留美、編集:EE Times Japan】

関連記事

微細化に堪え得るオンチップSRAM

微細化に堪え得るオンチップSRAM

ICの製造プロセスの微細化を進めるには、それに伴って生じる新たな課題に対処していかなければならない。そうした課題の1つが、プロセスばらつきの影響に堪え得るオンチップのSRAMを開発することである。今後も、SRAMの微細化トレンドを維持するためには、従来とは異なる技術的な工夫を盛り込む必要がある。 FinFETの父、「半導体業界は次の100年も続く」

FinFETの父、「半導体業界は次の100年も続く」

“FinFETの父”と呼ばれる研究者のChenming Hu氏は、Synopsysのユーザー向けイベントで、「半導体業界が次の100年も続くと確信している」と述べ、業界の未来が決して暗いものではないと主張した。同氏は新しいトランジスタのアイデアとして、NC-FET(負性容量トランジスタ)についても言及した。 磁気センサーの“異端児”がウェアラブルを変える

磁気センサーの“異端児”がウェアラブルを変える

超高感度磁気センサーの開発を手掛けるマグネデザインが、まったく新しい原理を採用した磁気センサー「GSR(GHz-Spin-Rotation)センサー」を開発した。現在最も普及している半導体センサーに比べて50倍の感度を実現している。 Intel、10nmプロセスでは新技術は導入せず

Intel、10nmプロセスでは新技術は導入せず

Intelは「ISSCC 2016」でムーアの法則の維持と“ポストCMOS”について講演し、10nmプロセスでは新しい技術は導入しないことを断言した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

Intelは、アナログ周辺回路をデジタル化して周辺回路に取り込もうとしている。これは温度センサーの回路設計の事例で、アナログトランジスタの代わりにBJTが、VCOの代わりにDCOが採用されている

Intelは、アナログ周辺回路をデジタル化して周辺回路に取り込もうとしている。これは温度センサーの回路設計の事例で、アナログトランジスタの代わりにBJTが、VCOの代わりにDCOが採用されている Intelはコアには従来のようにCMOSを使いつつ、周辺回路では新材料を採用した新たなデバイスアーキテクチャを用いるとした

Intelはコアには従来のようにCMOSを使いつつ、周辺回路では新材料を採用した新たなデバイスアーキテクチャを用いるとした