FPGAに不揮発メモリ技術応用、チップ面積を削減:カスタムLSIにFPGA機能を低コストで統合

東芝は、不揮発FPGAのチップ面積を削減し、価格低減を可能とする回路技術を開発した。従来のFPGA製品に比べて、同等機能をほぼ半分の回路面積で実現することが可能になるという。

FPGAの半分の回路面積で同等機能を実現

東芝は2016年6月、不揮発FPGAのチップ面積を削減し、価格低減を可能とする回路技術を開発したと発表した。開発した技術を応用すると従来のFPGA製品に比べて、同等機能をほぼ半分の回路面積で実現可能だという。

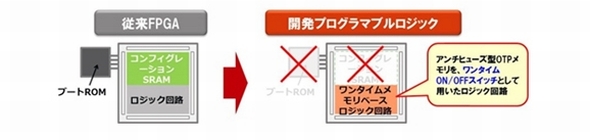

従来の一般的なFPGAは、回路情報を記憶するメモリセルの面積が比較的大きくなり、コスト高の一因となっていた。東芝は今回、FPGAを構成するロジック回路のスイッチ部に、アンチヒューズ型の不揮発ワンタイムメモリ素子を応用した高密度アレイスイッチを用いた。これにより、ロジック回路とメモリセルを一体化し、これまでに比べより小さな面積で回路設計を可能とした。

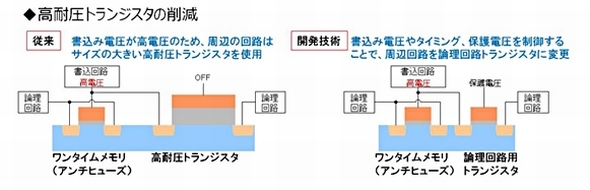

また、書き込みに高電圧を必要とするアンチヒューズ素子と、低電圧動作のロジック回路を、適切に接続するための回路を新たに開発した。具体的には、書き込み電圧やタイミング、保護電圧を制御することで、周辺回路を論理回路トランジスタに変更した。これによって、書き込み回路の周辺に必要となっていた高耐圧トランジスタの使用数を、従来の半分に抑えることが可能となり、チップ面積を削減することができたという。

東芝は、FPGA向けプログラミング用ソフトウェアも開発し、新たに開発した回路技術を用いたFPGAで機能ごとの面積を見積もった。その結果、これまでに比べてほぼ半分に縮小できることが分かったという。

東芝は、今回開発した回路技術を自社のカスタムLSIに組込み、2017年度以降にも実用化する考えである。今回の開発成果については、米国ホノルルで開催された半導体デバイスに関する国際会議「VLSI技術シンポジウム2016」で、その詳細を発表した。

関連記事

東芝、3D NAND新工場建設を決定

東芝、3D NAND新工場建設を決定

東芝は2016年3月17日、3次元構造のNAND型フラッシュメモリ専用工程に対応する新工場建設を決めた。 東芝の早期退職応募数は3449人

東芝の早期退職応募数は3449人

東芝は2016年4月15日、2016年3月下旬までの期間での募集していた早期退職優遇制度に3449人の応募があったと発表した。 東芝、18年度売上高5.5兆円に向けた事業計画

東芝、18年度売上高5.5兆円に向けた事業計画

東芝は2016年3月18日、2016年度(2017年3月期)事業計画説明会を開催し、2016年度に全事業を黒字化させるという経営再建策の進み具合と、2018年度売上高5兆5000億円、純利益1000億円を暫定目標に据えた成長戦略を発表した。 東芝、赤字転落の半導体事業は自主再建

東芝、赤字転落の半導体事業は自主再建

東芝の電子デバイス部門の2015年度(2016年3月期)業績は、550億円の営業赤字を計上する見込みとなった。前年度に比べ2716億円減という大幅減益だ。NAND型フラッシュメモリ(NANDメモリ)事業を除き、ディスクリート、システムLSI、ストレージの3事業で赤字となり、事業構造の見直しを実施する。さらに2015年後半からの売価下落で利益幅が縮小しているNANDメモリも、高集積品の開発を急ぎ価格競争力を高めるなどし、電子デバイス事業として2016年度の黒字転換を目指す。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(前編)

- 石炭灰から「レアアース元素」を回収、新日本繊維【訂正あり】

- Rapidus、IIM-1を「世界初の前/後工程一貫工場に」

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(後編)

- 「27年度後半の2nm量産誓う」 Rapidus、解析センター開設

- EVに吹く逆風 デンソーの焦りとロームが求める勝機とは

- 経産省、Rapidusに6315億円追加支援 「国益のため必ず成功」

- 光電融合チップレットの技術開発を開始 LSTCとimec

- 「技術を束ねて高価値システムに」 デンソーが2030年中計発表

- 京セラ、ウシオ電機の半導体レーザー事業を取得へ

開発した技術は、FPGAを構成するロジック回路のスイッチ部に、アンチヒューズ型の不揮発ワンタイムメモリ素子を応用した高密度アレイスイッチを用いた 出典:東芝

開発した技術は、FPGAを構成するロジック回路のスイッチ部に、アンチヒューズ型の不揮発ワンタイムメモリ素子を応用した高密度アレイスイッチを用いた 出典:東芝 高耐圧トランジスタの削減を可能としたことで、FPGAの高集積化を実現した 出典:東芝

高耐圧トランジスタの削減を可能としたことで、FPGAの高集積化を実現した 出典:東芝