新型TMR素子、室温環境でMR比92%を達成:待機電力ゼロのコンピュータ実現へ大きく前進

産業技術総合研究所の齋藤秀和企画主幹は、全単結晶トンネル磁気抵抗(TMR)素子を開発した。TMR素子の磁気抵抗変化率(MR比)は室温環境で92%と極めて大きい。待機電力ゼロのコンピュータを実現できる技術として期待される。

独自の成膜プロセスで、全単結晶TMR素子を作製

産業技術総合研究所(以下、産総研)スピントロニクス研究センター半導体スピントロニクスチーム付の齋藤秀和企画主幹は2016年9月、独自開発した単結晶酸化ガリウム(Ga2O3)の成膜プロセスを用いて、半導体Ga2O3をトンネル障壁層とした全単結晶トンネル磁気抵抗(TMR)素子を開発したと発表した。開発したTMR素子の磁気抵抗変化率(MR比)は室温環境で92%と極めて大きく、待機電力ゼロを可能とするコンピュータの実現に近づいた。

産総研はこれまで、新規TMR素子とそれを応用した磁気メモリの開発に取り組んできた。今回の研究では、半導体トンネル障壁層材料として、これまでほとんど注目されてこなかった酸化物半導体のGa2O3を用いた。この半導体は結晶構造が複雑で、一般的な強磁性電極と組み合わせた単結晶TMR素子の作製は難しいといわれてきたからだ。

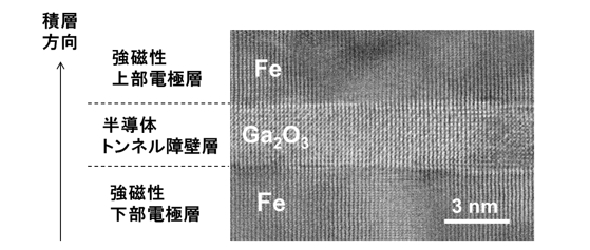

齋藤氏は、独自の成膜プロセスを開発して、Fe強磁性電極とGa2O3トンネル障壁層からなる全単結晶TMR素子を作製することに成功した。成膜には分子線エピタキシー法を用い、下部電極の単結晶Fe上に、厚みが0.4〜0.7nmの単結晶酸化マグネシウム(MgO)層を成長させた。

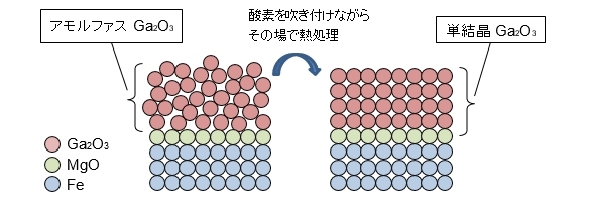

さらにその上に、厚みが1.5〜3.0nmのアモルファスGa2O3膜を室温環境で成膜した。その後、適量の酸素を膜に吹き付けつつ、500℃以下で熱処理を行ったところ、極めて高品位の単結晶Ga2O3膜を得ることができたという。この単結晶Ga2O3膜上には、単結晶Fe上部電極を直接成長させることが可能である。得られた単結晶Ga2O3膜を分析したところ、スピネル型という単純な結晶系の構造となっていることが分かった。

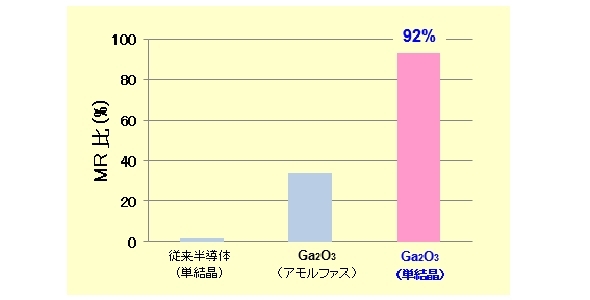

開発したTMR素子について、室温環境でのMR比を測定した。Ga2O3層を単結晶化することでMR比は92%となり、半導体トンネル障壁層の素子としてはこれまでで最も高い数値を示すことが分かった。MR比が増大したことについて齋藤氏は、トンネル障壁層と上部強磁性電極の単結晶化によって、電子が波の性質を保ったまま伝搬できるようになったことが大きな要因とみている。比較のため、従来の半導体障壁層をもつ全単結晶TMR素子(電極は強磁性金属)や、アモルファスGa2O3障壁層(上部電極のFeは多結晶)のTMR素子についても、室温環境におけるMR比を測定した。

齋藤氏らは、引き続きMR比の向上を図るとともに、Ga2O3膜に電界をかけて出力電流を制御するために必要となるゲート構造の設計およびその動作実証を行っていく。待機電力が不要な超省電力コンピュータの実現に向け、5年後をめどに実用的な性能を備えた縦型スピンFETを開発していく方針である。

関連記事

産総研、2030年に向けた研究戦略を策定

産総研、2030年に向けた研究戦略を策定

産業技術総合研究所(産総研)は、2030年に向けた産総研の研究戦略を策定した。2030年の産業像や社会像を見据え、「超スマート社会(Society 5.0)」の実現など、大きく4つの研究目標を定め開発に取り組む。 産総研、ナノ炭素材料の新しい合成法を開発

産総研、ナノ炭素材料の新しい合成法を開発

産業技術総合研究所の徐強上級主任研究員らは、棒状やリボン状に形状制御されたナノ炭素材料の新しい合成法を開発した。キャパシターの電極材料への応用などが期待されるナノ炭素材料を、高い収率で量産することが可能となる。 日本ゼオンと産総研、CNT実用化連携研究ラボを設立

日本ゼオンと産総研、CNT実用化連携研究ラボを設立

日本ゼオンと産業技術総合研究所は、カーボンナノチューブ(CNT)のより一層のコストダウンと生産量の工場を目指して、産総研つくばセンターに連携研究ラボを設立すると発表した。 アンテナ使わずセシウム原子で電磁波を測る技術

アンテナ使わずセシウム原子で電磁波を測る技術

産業技術総合研究所(産総研)は2016年7月11日、セシウム原子の共鳴現象を利用して電磁波の強度を測定する技術を開発したと発表した。一般的な電磁波測定で使われるアンテナが不要であり、電磁環境測定(EMC試験)の高度化や空間電磁界の可視化といった応用が期待できるという。 線幅0.8μmを実現する新原理の印刷技術を開発

線幅0.8μmを実現する新原理の印刷技術を開発

産業技術総合研究所(産総研)の山田寿一主任研究員らは、東京大学や山形大学、田中貴金属工業と共同で、線幅0.8μmの微細な電子回路を簡便に印刷できる技術を開発した。フレキシブルなタッチパネルセンサーなどへの応用を進めている。 リチウム硫黄電池、1500回充放電後も安定動作

リチウム硫黄電池、1500回充放電後も安定動作

産業技術総合研究所(産総研)の周豪慎氏らは、安定した充放電サイクル特性を持つリチウム硫黄電池の開発に成功した。電池のセパレーターに「イオンふるい」の機能を持つ複合金属有機構造体膜を用いることで実現した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「AI特需」の恩恵届かぬ日本企業 Gartnerが見る2026年半導体市場

- 「Rapidusの隣」に光電融合パッケージ開発拠点、28年度の完成目指す

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- シリコンフォトニクスと先進パッケージの統合が描く未来

- ルネサス26年1Qは増収増益 車載/AI好調で「足元は当面強い」

今回開発したTMR素子断面の電子顕微鏡写真 出典:産総研

今回開発したTMR素子断面の電子顕微鏡写真 出典:産総研 今回開発した単結晶Ga2O3膜の成膜方法 出典:産総研

今回開発した単結晶Ga2O3膜の成膜方法 出典:産総研 半導体障壁層が異なるTMR素子の室温環境におけるMR比の比較 出典:産総研

半導体障壁層が異なるTMR素子の室温環境におけるMR比の比較 出典:産総研