高性能コンピューティング向けの2.nD(2.n次元)パッケージング技術:福田昭のデバイス通信(105) TSMCが解説する最先端パッケージング技術(4)(1/2 ページ)

2012年ごろから、主に高性能コンピューティング(HPC)分野では「CoWoS(Chip on Wafer on Substrate)」の製品化が進んだ。その最大の特長であるシリコンインターポーザは優れた技術なのだが、コストが高いのが難点だった。そのため、CoWosの低コスト版ともいえる2.nD(2.n次元)のパッケージング技術の提案が相次いだ。

シリコンインターポーザによるコストの上昇

2016年12月に開催された国際学会IEDMのショートコース講演(技術解説講演)から、「システム集積化に向けた最先端パッケージング技術(Advanced Packaging Technologies for System Integration)」と題する講演の概要をシリーズでご紹介している。講演者はシリコンファウンドリー最大手のTSMCでシニアディレクターを務めるDouglas Yu氏である。なお講演内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、Yu氏の講演内容を筆者が適宜、補足している。あらかじめご了承されたい。

前回は、TSMCが開発してきた2種類の2.5D(2.5次元)パッケージング技術、「CoWoS(Chip on Wafer on Substrate)」技術と「InFO(Integrated Fan-Out wafer level packaging)」技術を簡単に紹介した。

Yu氏の講演は、前回までが序論に相当する。今回からは本論に入る。本論の前半は高性能コンピューティング(HPC)向けパッケージング技術、本論の後半はモバイル向けパッケージング技術である。

ここからは、高性能コンピューティング(HPC)向けパッケージング技術の解説をご紹介する。2.5D(2.5次元)あるいは2.nD(2.n次元)などと呼ばれる新世代のパッケージング技術は、TSMCが開発した「CoWoS(Chip on Wafer on Substrate)」から始まったといえる。CoWoS技術は主に高性能コンピューティング(HPC)分野で2012年ころから製品化されてきた。

前回で述べたように、CoWoS技術の最大の特徴は、「シリコンインターポーザ(Silicon Interposer)」と呼ぶ中間的な基板の導入にある。シリコンインターポーザは優れたソリューションなのだが、大面積のシリコンダイを使うことによる製造コストの上昇は、歓迎された訳ではない。

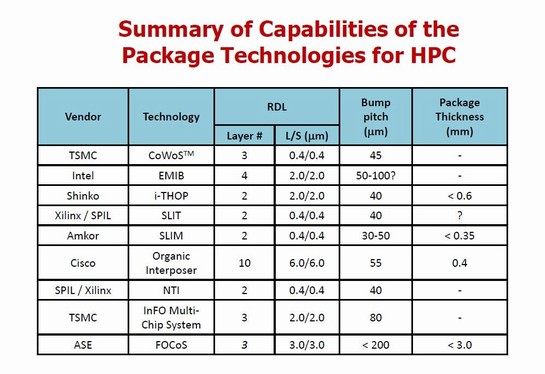

このため、CoWoS技術の登場以降はその低コスト版と呼べる、2.nD(2.n次元)のパッケージング技術を他社が相次いで提案していった。その主眼は、シリコンインターポーザの導入によるコストの上昇を抑えながらも、高密度な配線によって複数のシリコンダイを密接に並べることにある。

低コスト版2.nD(2.n次元)パッケージング技術の流れを大まかに述べると、インターポーザとなるシリコンの面積を小さくしたり、インターポーザの材料をシリコンではなく樹脂に換えたりする試みがまず、現れた。さらには、インターポーザそのものを省く試みがいくつか、提案されていった。

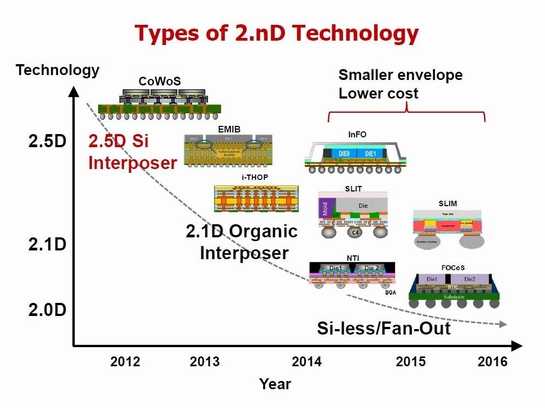

CoWoS技術以降の高性能コンピューティング向け2.nD(2.n次元)パッケージング技術の流れ。ここに挙げたパッケージング技術には試作レベル(あるいは学会発表レベル)にとどまり、製品化されなかったものが含まれているので留意されたい(クリックで拡大) 出典:TSMC

CoWoS技術以降の高性能コンピューティング向け2.nD(2.n次元)パッケージング技術の流れ。ここに挙げたパッケージング技術には試作レベル(あるいは学会発表レベル)にとどまり、製品化されなかったものが含まれているので留意されたい(クリックで拡大) 出典:TSMCCopyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増