モバイル端末向けの最先端パッケージング技術:福田昭のデバイス通信(110) TSMCが解説する最先端パッケージング技術(9)

今回から、モバイル端末向けのパッケージング技術について解説する。大きく分けて、ウエハーレベルのファンアウトパッケージング(FOWLP)、パネルレベルのファンアウトパッケージング(FOPLP)、プリント基板へ回路素子を埋め込むパッケージング(ESP)がある。まずは、パッケージング技術における「ファンアウト」の意味を確認しつつ、Infineon Technologiesが開発した“元祖FOWLP”を説明したい。

3種類のモバイル端末向けパッケージング技術

2016年12月に開催された国際学会IEDMのショートコース講演(技術解説講演)から、「システム集積化に向けた最先端パッケージング技術(Advanced Packaging Technologies for System Integration)」と題する講演の概要をシリーズでご紹介している。講演者はシリコンファウンダリ最大手のTSMCでシニアディレクターを務めるDouglas Yu氏である。なお講演内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、Yu氏の講演内容を筆者が適宜、補足している。あらかじめご了承されたい。

前回は、Intelが開発した、2.nD(2.n次元)の高性能・高密度パッケージング技術「EMIB(Embedded Multi-die Interconnect Bridge)」の概要をご報告した。EMIBは高性能コンピューティング向けのパッケージング技術として製品化されている。

今回からは、モバイル端末向けの最先端パッケージング技術に関する講演パートに入ろう。講演パートは大きく3つに分かれている。始めは、ウエハーレベルのファンアウトパッケージング(FOWLP:Fan Out Wafer Level Packaging)技術、次は、パネルレベルのファンアウトパッケージング(FOPLP:Fan Out Panel Level Packaging)技術、最後はプリント基板へ回路素子を埋め込むパッケージング(ESP:Embedded Substrate Packaging)技術である。

「ファンアウト」の意味

上記3種類のパッケージング技術の中で、最初の2つには「ファンアウト」の語句が入っている。ここで「ファンアウト」とは、論理回路素子(NANDやNORなど)の出力数(ファンアウト)ではない。同様にパッケージング技術には「ファンイン」という用語が存在する。これも論理回路素子の入力数(ファンイン)ではない。まったく違う意味の単語なので、確認しておく。

パッケージング技術で「ファンアウト」と「ファンイン」とは、シリコンダイの入出力パッドから、どのように配線を引き回してパッケージの入出力端子にレイアウトするかの違いを指す。「ファンアウト」だとパッケージの入出力端子はシリコンダイよりも大きな面積に展開される。シリコンダイとパッケージをつなぐ配線群は、シリコンダイの外側に引き回される。上から見ると、入出力端子が外側に広がっているように見えるので、「ファンアウト」と呼ぶ。

「ファンイン」は、「ファンアウト」タイプのパッケージング技術が登場したことによって、従来のウエハーレベル・チップスケールパッケージ(WLCSP)を指す用語として生まれた。シリコンダイの入出力パッドは周辺あるいはエリアに配置されているのに対し、パッケージの入出力端子はエリアアレイ配置になっている。配線群はシリコンダイの内側に引き回される。上からみると、シリコンダイの周辺から内側にパッケージの入出力端子がすぼまっていくように見えるので、「ファンイン」と呼ぶ。

従来の超小型パッケージング技術であるWL-CSP(ファンインタイプのウエハーレベルパッケージ)には、シリコンダイとプリント基板の熱膨張係数の違いによってパッケージの大きさが限定されるという制約があった。約6mm角前後が、WL-CSPの最大寸法である。このため、数多くの入出力端子を収容できない、複数のシリコンダイを搭載できない、といった弱点を抱えていた。

これに対してファンアウトのウエハーレベルパッケージング技術、すなわちFOWLP技術は、パッケージの入出力端子を配置する領域が広いので、数多くの入出力端子を収容できる。さらに、複数のシリコンダイを搭載可能である。

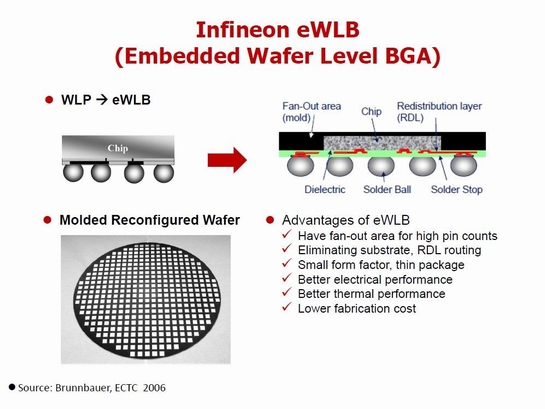

Infineon Technologiesが開発したFOWLP技術の元祖「eWLB」

最初のFOWLP技術は、半導体メーカーのInfineon Technologiesが2006年に開発したeWLB(embedded Wafer Level Ball grid array)技術である。eWLB技術は、現在まで連なるFOWLP技術の基本要素をおおむね、備えていた。すなわち、ファンアウト構造による多ピン対応、再配置配線構造を備えながらも樹脂基板が存在しない、パッケージの外形寸法が極めて低い(薄い)、電気的な特性に優れている、放熱特性が良好である、などだ。

eWLB技術によるパッケージの再配置配線層は2層構造で、配線幅/間隔は10μm/10μm、配線金属は銅(Cu)である。パッケージの入出力端子はハンダボールで、ピッチは0.5mm。パッケージの大きさは12mm角である。パッケージの高さは0.5mmしかない。この薄さが、モバイル端末向けのパッケージング技術として適している大きな理由である。

従来技術(WL-CSP技術)(左上)とFOWLP技術(eWLB技術)(右上)。「再構成ウエハー(Reconfigured Wafer)」(左下)と呼ぶ、樹脂封止済みウエハーに再配置配線(RDL)層をウエハー処理プロセスで一括形成する 出典:TSMC(クリックで拡大)

従来技術(WL-CSP技術)(左上)とFOWLP技術(eWLB技術)(右上)。「再構成ウエハー(Reconfigured Wafer)」(左下)と呼ぶ、樹脂封止済みウエハーに再配置配線(RDL)層をウエハー処理プロセスで一括形成する 出典:TSMC(クリックで拡大)(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

「SEMICON West 2016」、Synopsysが予測する5nm世代のトランジスタ技術

「SEMICON West 2016」、Synopsysが予測する5nm世代のトランジスタ技術

Synopsysの講演では、5nm世代のトランジスタのシミュレーション評価結果が報告された。この結果からはFinFETの限界が明確に見えてくる。5nm世代に限らず、プロセスの微細化が進むと特に深刻になってくるのが、トランジスタ性能のばらつきだ。 シリコンが次の手、村田製作所のキャパシター戦略

シリコンが次の手、村田製作所のキャパシター戦略

2016年10月に村田製作所が買収したフランスのIPDiAは、シリコンキャパシターを事業として手掛けるほぼ唯一のメーカーだ。積層セラミックコンデンサーに比べてかなり高価なシリコンキャパシターは、その用途は限られている。それにもかかわらず、なぜ村田製作所はIPDiAの買収に至ったのか。 Samsungの売上高がIntelを超える可能性も

Samsungの売上高がIntelを超える可能性も

DRAMとNANDフラッシュメモリの価格が上昇していることから、2017年第2四半期(4〜6月期)におけるSamsung Electronicsの売上高が、Intelを超える可能性が出てきた。 ムーアの法則の“新たな意味”とは

ムーアの法則の“新たな意味”とは

台湾半導体産業協会の専門家は、今後ムーアの法則は、「半導体の集積率の向上」というよりも、より実質的な意味を持つようになると指摘する。3次元構造やTSMCの「InFO」のようなパッケージング技術によって性能の向上を図っていくというものである。 半導体市場における中国の脅威、米政府が報告

半導体市場における中国の脅威、米政府が報告

半導体産業における中国の脅威について、米政府が報告書をまとめた。中国政府の半導体強化政策を批判しているわけではなく、中国企業による米国半導体企業の買収が、米国の安全を脅かすものになり得る場合もあると指摘し、中国メーカーが市場をゆがめるようなM&A政策を採った場合は、これを阻止するよう提言している。 TSMCが7nmなど最新プロセスの開発状況を報告(前編)

TSMCが7nmなど最新プロセスの開発状況を報告(前編)

TSMCは2017年3月15日(米国時間)にカリフォルニア州で開催したイベント「TSMC Technology Symposium」で、最先端プロセスの開発状況を報告した。その発表からは、FD-SOIプロセスへの対抗心が垣間見えた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待