富士電機、トレンチゲート構造のSiC-MOSFET:電気抵抗は半分以下に

富士電機は、トレンチゲート構造の「SiC-MOSFET」を開発した。プレーナーゲート構造を用いた素子に比べて、電気抵抗は5割以上も小さくなる。

オールSiCモジュールも2017年度中に製品化へ

富士電機は2017年7月、トレンチゲート構造の「SiC-MOSFET」を開発したと発表した。プレーナーゲート構造を用いた素子に比べて、電気抵抗は5割以上も小さくなる。

SiC(炭化ケイ素)パワー半導体は、現在主流となっているSi(シリコン)パワー半導体に比べて、電力損失が小さい。このため、搭載機器の省エネにつながると期待されている。同社は2013年10月より、松本工場(長野県松本市)内にSiCパワー半導体の生産ラインを立ち上げるなど、デバイスの開発、量産と応用機器への搭載にいち早く取り組んできた。

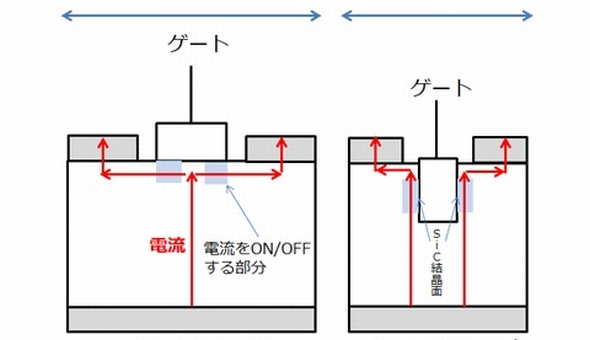

同社は今回、産業技術総合研究所との共同研究による成果を活用し、トレンチゲート構造を用いたSiC-MOSFETを開発した。この方式はウエハーに溝を掘り、垂直方向に電流経路を作る構造である。電流経路を水平方向に作るプレーナーゲート構造に比べて、セルの幅を短くすることができる。このため、同一の素子サイズで、多くのセルを搭載することができ、より多くの電流を流すことが可能となる。

トレンチゲート構造のトランジスタでは、電流をオン、オフするゲートの結晶面における電気抵抗をいかに下げるかが重要となる。今回は、独自技術を用いて信頼性を維持しつつ、しきい値電圧が5Vで3.5mΩcm2という電気抵抗を達成した。この数値は、プレーナーゲート構造の素子に比べて半分以下だという。

同社は、開発したトレンチゲート構造のSiC-MOSFET素子とSiC-SBD(ショットキーバリアダイオード)で構成するオールSiCモジュールについて、2017年度中をめどに製品化する予定である。このオールSiCモジュールを出力7.5kW、周波数20kHzのインバーターに搭載すると、SiベースのIGBTモジュールを用いた場合に比べて、電力損失を78%も削減することが可能になるという。

関連記事

パワー半導体市場、2025年に酸化ガリウムがGaNを抜く

パワー半導体市場、2025年に酸化ガリウムがGaNを抜く

富士経済が、2025年における次世代パワー半導体市場の予測を発表した。SiC、GaNはともに堅調に成長する。加えて有望視されているのが酸化ガリウム系パワー半導体だ。特に中高耐圧領域での優位性が際立ち、2025年には、市場規模でGaNパワー半導体を上回るとみられる。 SiC向け銀ナノペースト、低加圧接合が可能に

SiC向け銀ナノペースト、低加圧接合が可能に

新エネルギー・産業技術総合研究所(NEDO)は、「nano tech 2017」で、SiCパワーモジュール向けに、銀ナノペーストを用いた接合材を展示した。NEDOのプロジェクトとしてDOWAエレクトロニクスが開発したもの。 三菱電機がSiC-SBDを発売、ディスクリート品は初

三菱電機がSiC-SBDを発売、ディスクリート品は初

三菱電機は、SiC(炭化ケイ素)を用いたパワー半導体の新製品「SiC-SBD」を2017年3月1日に発売した。同社はこれまでSiC-SBDやSiC-MOSFETを搭載したパワー半導体モジュールを2010年から製品化してきたが、ディスクリート品の提供は初となる。 SiCだけではない、パワー製品群の展示に注力 ローム

SiCだけではない、パワー製品群の展示に注力 ローム

ロームは、パワー半導体の展示会「PCIM Europe 2017」(2017年5月16〜18日、ドイツ・ニュルンベルク)にて、Si-IGBTやSiC-MOSFET向けゲートドライバーICなどを展示した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 加賀電子が新光商事にTOB、完全子会社化へ

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

- SiC LSIの事業化に挑む 28年以降ADCのサンプル出荷へ

- AIの「トンデモ判断」で本番DBが全飛び! 他山の石にしたいAIコーディングの落とし穴

- サンケン電気26年3月期は赤字転落 中国の「自前主義」響く

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

トレンチゲート構造を用いたSiC-MOSFET素子の外観

トレンチゲート構造を用いたSiC-MOSFET素子の外観 プレーナーゲート構造(左)とトレンチゲート構造(右)のセル断面イメージ図 出典:富士電機

プレーナーゲート構造(左)とトレンチゲート構造(右)のセル断面イメージ図 出典:富士電機 製品化を目指すオールSiCモジュールの外観

製品化を目指すオールSiCモジュールの外観