FeRAMのメモリセル構造の基礎:福田昭のストレージ通信(67) 強誘電体メモリの再発見(11)(1/2 ページ)

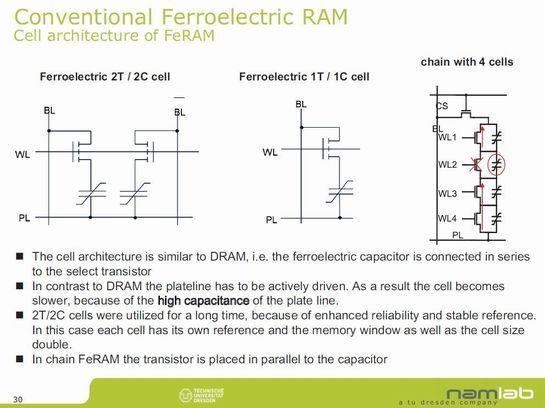

強誘電体不揮発性メモリ(FeRAM)の構造には、2T2C方式、1T1C方式、チェインセル方式がある。それぞれの特徴を紹介するとともに、メモリセルの断面構造についても解説しよう。

2T2C方式、1T1C方式、チェインセル方式

前回は、強誘電体不揮発性メモリ(FeRAM)の基本動作である、データの書き込み動作と読み出し動作を簡単に説明した。今回は、FeRAMのメモリセル構造について簡単に解説する。

FeRAMのメモリセル構造は、「DRAMに似ている」といわれることが多い。DRAMのメモリセルは、1個のセル選択トランジスタ(MOSFET)と1個の高誘電体キャパシターで構成される。FeRAMのメモリセルは、同様に、1個のセル選択トランジスタと1個の高誘電体キャパシターで構成される。

ただしFeRAMセルでは、キャパシターの絶縁膜は高誘電体であるとともに、強誘電体である。従ってキャパシターの働きが違う。DRAMのキャパシターは単に電荷を蓄えておく(それも一時的にだけ)のに対し、FeRAMのキャパシターは分極を恒久的に維持するとともに、無限に近い膨大な回数の分極反転を要求される。

このためFeRAMでは、2個のメモリセルをペアとして1個のデータを保存する、2T2C方式のメモリセルが一般的である。ワード線を1本、ビット線を2本(1対)とし、ワード線を共有する一方の1T1Cセルが「ビット線(BL)」に、もう一方の1T1Cセルが「ビット線バー(BL/)」につながる。

対となるメモリセルには、異なる極性のデータを書き込む。例えばビット線のセルに「正(プラス)」方向の残留分極を書き込んだときは、ビット線バーのセルには「負(マイナス)」方向の残留分極を書き込む。

2T2C方式のメモリセルでデータを読み出すときは、ワード線に電圧を加える。すると、どちらかのキャパシターだけに、分極反転が必ず起こる。分極反転に伴い、ビット線とビット線バーのどちらかの電圧が上昇する。

2T2C方式の非常に優れている点は、データの読み出しが安定していることと、動作の繰り返しに強い(動作寿命が長い)ことである。強誘電体材料には、分極反転を繰り返すと残留分極が小さくなるという「疲労(ファティーグ)」と呼ばれる独特の性質がある。後述するが、2T2C方式は「疲労」が起きにくい。

これに対して1T1C方式は、DRAMに近い高密度なメモリセルアレイを実現できる。2T2C方式ではメモリセルの構成に必要な素子の数が多く、高密度化には向かない。1T1C方式であれば、素子数が少なく、メモリの大容量化と高密度化が可能に見える。

ただし1T1C方式には、大きな弱点が存在する。参照用セル(リファレンスセル)を必要とすることである。読み出した信号を判別するためには、一定の値(参照値)よりも高いか低いかを検知しなければならない。このために1T1C方式では、参照用の1T1Cセルを設け、両方の電圧を比較することでデータの高低を判別する。ところが、参照用セルは読み出し動作ごとに破壊読み出しとなるので、他のセルに比べると「疲労」が著しく早く進む。この結果、実用的に十分な読み出し回数および書き込み回数を得られなくなってしまう。

この点、2T2C方式は参照用セルを持たない。ペアとなるセルがおおむね均等に疲労していくので、信号の劣化が少なく、動作可能な回数(寿命)が長い。

1T1C方式よりも高い密度を狙ったのが、チェインセルである。トランジスタとキャパシターを並列に接続したペアを作り、このペアを縦に接続する。ただし密度は上がるものの、動作の速度は低下する。このためペアを縦に積む数は、それほど多くできない。例えば4つ、8つといった数にとどまる。またメモリセルの構造はどうしても、複雑化する。製造は、どうしても難しくなる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- メモリも中国が猛追 YMTCは新工場建設

- 560億ドル投資でも「需要に追い付けない」 AI急成長でTSMC表明

- 「AI特需」の恩恵届かぬ日本企業 Gartnerが見る2026年半導体市場

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- SAIMEMORYの垂直ビルド構造メモリ開発がNEDO採択

- 「Rapidusの隣」に光電融合パッケージ開発拠点、28年度の完成目指す

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- 半導体用の「沸騰冷却技術」 アプライドと九州大が実用化目指す