従来型材料を使った強誘電体トランジスタの研究開発(後編):福田昭のストレージ通信(75) 強誘電体メモリの再発見(19)(2/2 ページ)

» 2017年09月12日 11時30分 公開

[福田昭,EE Times Japan]

64kビットの不揮発性メモリを強誘電体トランジスタで試作

それから3年後の2011年9月に産総研は、強誘電体トランジスタで記憶容量が64kビットの不揮発性メモリを試作したと、報道機関向けにリリース発表した。これも、産総研の酒井滋樹氏を中心とする研究グループと、東京大学の竹内健准教授を中心とする研究グループの、共同研究成果である。

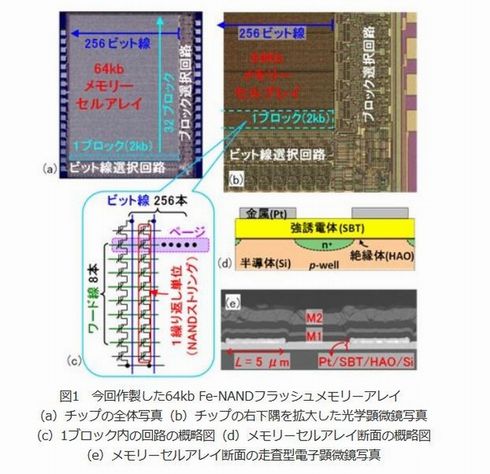

試作した不揮発性メモリの特長は、NANDフラッシュメモリと同様のメモリセルアレイ構造を採用したことだ。8個の強誘電体トランジスタをNAND接続し、1本のメモリストリングを構成した。強誘電体トランジスタの構造は、2008年5月に発表したものと基本的には変わらない。トランジスタのゲート長とゲート幅はともに5μmである。

産総研と東京大学が共同開発した64kビットの強誘電体不揮発性メモリ。NAND構造の強誘電体トランジスタ(FeFET)をメモリセルに採用した。出典:産業技術総合研究所(参考リリース) (クリックで拡大)

産総研と東京大学が共同開発した64kビットの強誘電体不揮発性メモリ。NAND構造の強誘電体トランジスタ(FeFET)をメモリセルに採用した。出典:産業技術総合研究所(参考リリース) (クリックで拡大)試作した64kビットのメモリセルアレイの不良率は29.6%である。2kビットずつのブロックレベルでは、不良率は19%だった。正常に動作するメモリセルを対象に2kビットのブロックでデータ保持特性をテストしたところ、2日間のデータ保持期間を確認できた。なおデータ書き込みに必要な電圧はワード線が6V、ビット線が1Vである。

残念ながら、強誘電体トランジスタを使った不揮発性メモリは現在のところ、製品とはなっていない。今後の発展に期待したい。

(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

関連記事

新材料「二酸化ハフニウム」を使った強誘電体メモリへの長い道

新材料「二酸化ハフニウム」を使った強誘電体メモリへの長い道

今回から2回にわたり、強誘電体の二酸化ハフニウムが、不揮発性メモリ用のキャパシターとしてどのような特性を示しているかを解説する。強誘電体不揮発性メモリ(FeRAM)のメモリセルで重要なのは、強誘電体キャパシターの特性だ。二酸化ハフニウムを絶縁膜とする強誘電体キャパシターが、優れた特性を備えているかどうかを調べる必要がある。 FeRAMのメモリセル構造の基礎

FeRAMのメモリセル構造の基礎

強誘電体不揮発性メモリ(FeRAM)の構造には、2T2C方式、1T1C方式、チェインセル方式がある。それぞれの特徴を紹介するとともに、メモリセルの断面構造についても解説しよう。 東芝、岩手県北上市にメモリ新工場建設へ

東芝、岩手県北上市にメモリ新工場建設へ

東芝は2017年9月6日、NAND型フラッシュメモリの新製造拠点を岩手県北上市に建設する予定であると発表した。 大型パネルで大量のパッケージを一括組み立てする「FOPLP」技術

大型パネルで大量のパッケージを一括組み立てする「FOPLP」技術

前回説明したウエハーレベルのファンアウトパッケージング技術「FOWLP(Fan Out Wafer Level Packaging)」における一括製造の考え方を、パネル状の基板に適用したのが、パネルレベルのファンアウトパッケージング技術「FOPLP(Fan-Out Panel Level Packaging)」だ。今回は、FOPLPの強みや、どんなパッケージングに適しているかなどを説明する。 シリコンインターポーザを導入した高性能パッケージの製品例

シリコンインターポーザを導入した高性能パッケージの製品例

シリコンインターポーザを導入したパッケージの製品化時期は、おおむね、2012年の第1期と、2015〜2016年の第2期に分けられる。それぞれの時期を代表する製品例と、それらの特徴を紹介する。 投資ファンドによるLattice買収、破談が濃厚に

投資ファンドによるLattice買収、破談が濃厚に

未公開株式投資ファンドCanyon Bridge Capital Partnersによる、米FPGAメーカーのLattice Semiconductor(ラティス・セミコンダクター)の買収が、破談になる可能性が高まった。米国の外国投資委員会(CFIUS)が、米大統領に、本案件を中止または禁止するよう勧告したという。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- Intelがアイルランド工場を完全子会社化、Apolloから49%買い戻し

- 次世代パワー半導体向け接合材を開発、エレファンテック

Special SitePR

あなたにおすすめの記事PR