シリコンインターポーザを導入した高性能パッケージの製品例:福田昭のデバイス通信(108) TSMCが解説する最先端パッケージング技術(7)(1/2 ページ)

シリコンインターポーザを導入したパッケージの製品化時期は、おおむね、2012年の第1期と、2015〜2016年の第2期に分けられる。それぞれの時期を代表する製品例と、それらの特徴を紹介する。

2012年から始まったシリコンインターポーザ技術の製品化

2016年12月に開催された国際学会IEDMのショートコース講演(技術解説講演)から、「システム集積化に向けた最先端パッケージング技術(Advanced Packaging Technologies for System Integration)」と題する講演の概要をシリーズでご紹介している。講演者はシリコンファウンドリー最大手のTSMCでシニアディレクターを務めるDouglas Yu氏である。なお講演内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、Yu氏の講演内容を筆者が適宜、補足している。あらかじめご了承されたい。

前回は、TSMCが開発した高性能・高密度パッケージング技術「CoWoS(Chip on Wafer on Substrate)」の構造と製造工程を説明した。今回は、CoWoS技術を含めた、シリコンインターポーザ技術のパッケージを製品化した事例をご報告する。

製品化の時期はおおむね、2つに分かれている。2012年の第1期と、2015年〜2016年の第2期である。

ロジックダイの分割搭載と、ロジックとメモリ混載にCoWoSを適用

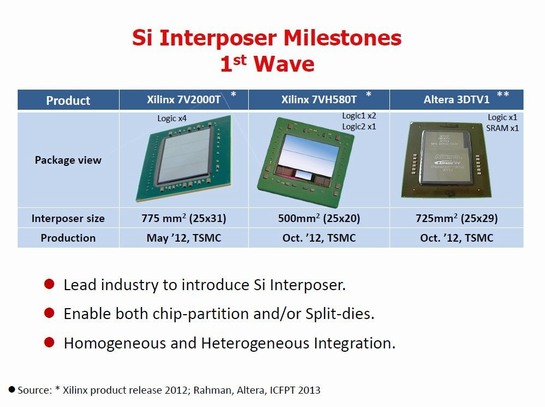

2012年の第1期では、FPGAの大手ベンダーであるXilinxとAltera*)がそれぞれ、ハイエンドの製品シリーズ向けにTSMCのCoWoS技術を採用した。

*)旧Alteraの製品は、Intelが2015年12月にAlteraを買収したことにより、現在は「Intel FPGA」ブランドとして販売されている。

Xilinxは28nm世代のFPGA「Virtex-7」シリーズの「2000T」に、4枚の同一サイズのFPGAロジックダイをシリコンインターポーザに近接して搭載したパッケージを導入した(関連記事:「ザイリンクス、28nm世代の次期FPGAで3次元パッケージを採用」)。同社は「Virtex-7」シリーズの「7 VH580T」にも、大きなロジックダイ(FPGA)を2枚と小さなロジックダイ(トランシーバー)を1枚、シリコンインターポーザに近接して搭載したパッケージを導入している。Alteraは、FPGAシリコンダイとSRAMシリコンダイをシリコンインターポーザに搭載した(関連記事:「“シリコンコンバージェンス”へ、3次元FPGAの取り組みをAlteraが説明」)。

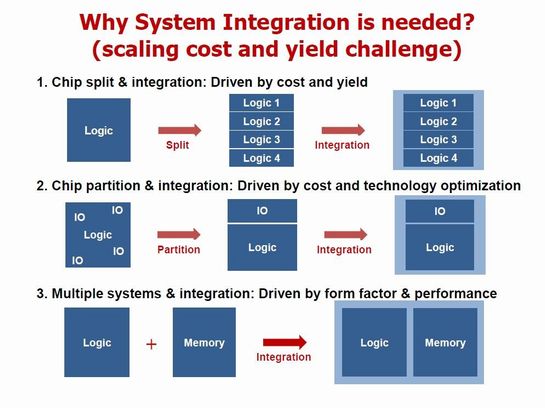

XilinxとAlteraの違いは、Xilinxがワンチップには収容困難なほど大規模なFPGAロジックを複数のシリコンダイに分割していることに対し、Alteraはロジックとメモリという異なる種類のシリコンダイを集積していることにある。下記にも示したが、本シリーズの第2回で説明した図面の1番がXilinxの事例、3番がAlteraの事例に対応していることが分かる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増