ISSCC媄弍島墘偺弶擔屵屻僴僀儔僀僩乮偦偺1乯丄僾儘僙僢僒偲傾僫儘僌偺嵟愭抂媄弍丗暉揷徍偺僨僶僀僗捠怣乮126乯 2寧奐嵜梊掕偺ISSCC 2018傪僾儗價儏乕乮2乯乮1/2 儁乕僕乯

乽ISSCC 2018乿媄弍島墘偺弶擔乮2018擭2寧12擔乯丅屵屻偺僴僀儔僀僩偼丄嵟愭抂偺僾儘僙僢僒偍傛傃傾僫儘僌媄弍偺榑暥敪昞偩丅僾儘僙僢僒偱偼丄Intel傗IBM丄AMD偑丄傾僫儘僌媄弍偱偼Qualcomm傗MediaTek偑丄偦傟偧傟偺尋媶惉壥傪斺業偡傞丅

寧梛擔偺屵屻偐傜媄弍島墘僙僢僔儑儞偑巒傑傞

丂慜夞偐傜丄2018擭乮棃擭乯2寧偵暷崙僒儞僼儔儞僔僗僐偱奐嵜梊掕偺敿摫懱夞楬媄弍偵娭偡傞崙嵺妛夛丄乽ISSCC 2018乿偺奣梫傪僔儕乕僘偱偍撏偗偟偰偄傞丅崱夞偼丄儊僀儞僀儀儞僩偱偁傞媄弍島墘僙僢僔儑儞偺弶擔乮2寧12擔乯屵屻偐傜丄僴僀儔僀僩傪偛徯夘偟傛偆丅

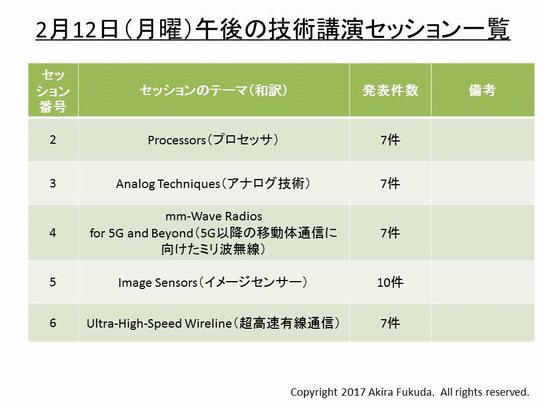

丂慜夞偱偛愢柧偟偨傛偆偵丄弶擔偺屵慜偼僾儗僫儕島墘僙僢僔儑儞偱偁傞丅偦偺屻丄拫怘媥宔乮儔儞僠偼採嫙偝傟側偄乯傪嫴傫偱丄屵屻1帪30暘偐傜堦斒偺媄弍島墘僙僢僔儑儞偑巒傑傞丅僙僢僔儑儞斣崋偩偲丄僙僢僔儑儞2偐傜僙僢僔儑儞6傑偱偺5杮偺島墘僙僢僔儑儞偑摨帪暲峴偱恑傓丅僙僢僔儑儞柤偼丄僾儘僙僢僒乮僙僢僔儑儞2乯丄傾僫儘僌媄弍乮僙僢僔儑儞3乯丄5G埲崀偺堏摦懱捠怣偵岦偗偨儈儕攇柍慄乮僙僢僔儑儞4乯丄僀儊乕僕僙儞僒乕乮僙僢僔儑儞5乯丄挻崅懍桳慄捠怣乮僙僢僔儑儞6乯丄偱偁傞丅

Intel丄IBM丄AMD偑嵟愭抂偺僾儘僙僢僒媄弍傪斺業

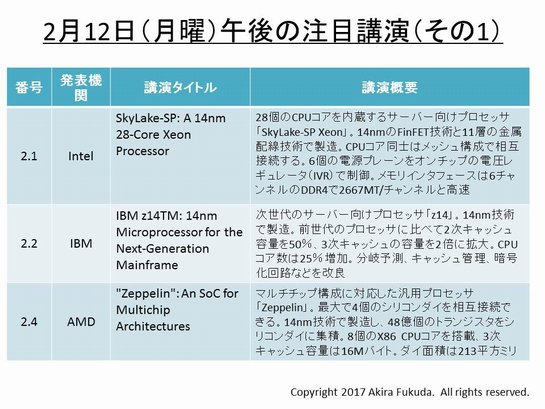

丂偙偺帪娫懷偺拲栚偡傋偒島墘偼傑偢丄僙僢僔儑儞2偺乽僾儘僙僢僒乿偩傠偆丅Intel丄IBM丄AMD偑嵟愭抂偺僾儘僙僢僒媄弍傪斺業偡傞丅

丂Intel偼28屄偲悢懡偔偺x86 CPU僐傾傪撪憼偡傞僒乕僶梡僾儘僙僢僒乽SkyLake-SP Xeon乿偺夞楬媄弍傪敪昞偡傞乮島墘斣崋2.1乯丅14nm悽戙偺FinFET媄弍偲11憌偺嬥懏攝慄媄弍偵傛偭偰惢憿偡傞丅28屄偺CPU僐傾偼丄儊僢僔儏峔惉偱憡屳愙懕偝傟傞丅暋悢偺揹埑儗僊儏儗乕僞乕傪撪憼偟偰偍傝丄6屄偺揹尮僾儗乕儞傪惂屼偡傞丅儊儌儕僀儞僞僼僃乕僗偼6僠儍儞僱儖偺DDR4偱丄揮憲懍搙偼2667MT/僠儍儞僱儖偲崅懍偱偁傞丅

丂IBM偼丄師悽戙偺僒乕僶岦偗僾儘僙僢僒乽z14乿偺夞楬媄弍傪岞昞偡傞乮島墘斣崋2.2乯丅14nm媄弍偱惢憿偡傞丅摦嶌廃攇悢偼慜悽戙偺僾儘僙僢僒偵斾傋偰200MHz傎偳岦忋偟偨丅傑偨丄2師僉儍僢僔儏偺梕検傪50亾丄3師僉儍僢僔儏偺梕検傪2攞偵奼戝偟偨丅CPU僐傾悢偼慜悽戙偵斾傋偰25亾憹壛偟偰偄傞丅暘婒梊應丄僉儍僢僔儏娗棟丄埫崋壔夞楬側偳傪夵椙偟偨丅

丂AMD偼丄嵟怴儅僀僋儘僾儘僙僢僒乽Zeppelin乿偺夞楬媄弍傪曬崘偡傞乮島墘斣崋2.4乯丅乽Zeppelin乿偼斈梡惈偑崅偔丄僒乕僶偐傜僴僀僄儞僪偺僨僗僋僩僢僾PC丄儊僀儞僗僩儕乕儉偺僨僗僋僩僢僾PC傑偱傪僇僶乕偡傞丅嵟戝偱4枃偺僔儕僐儞僟僀傪憡屳偵愙懕偱偒傞丅僔儕僐儞僟僀偼14nm媄弍偱惢憿偡傞丅僩儔儞僕僗僞悢偼48壄屄偱偁傞丅僔儕僐儞僟僀柺愊偼213mm2丅x86傾乕僉僥僋僠儍偺CPU僐傾傪8屄搵嵹偡傞丅3師僉儍僢僔儏偺梕検偼16M僶僀僩丅儊儌儕惂屼夞楬偲擖弌椡惂屼夞楬丄僒僂僗僽儕僢僕夞楬傪撪憼偡傞丅

Copyright © ITmedia, Inc. All Rights Reserved.

婰帠儔儞僉儞僌

- 乽悽奅弶乿惉壥偱1000憌挻3D僼儔僢僔儏偵摴嬝丄僉僆僋僔傾偲Sandisk

- 僜僯乕敿摫懱丄26擭搙偼尭廂尒崬傒 儊儌儕巗嫷晄摟柧

- 僫僼僒婋婡偱敆傞乽儗僕僗僩嫙媼搑愨乿乗乗悽奅偺敿摫懱岺応傪掆巭偝偣傞丄傕偆堦偮偺椪奅揰

- 儁儘僽僗僇僀僩乛CIGS僞儞僨儉懢梲揹抮偱乽悽奅嵟崅乿岠棪払惉丄搶嫗搒巗戝傜

- 乽夋慺偺惢憿傕僷乕僩僫乕偲乿廫帪巵偑岅傞丄僜僯乕亊TSMC崌曎偺慱偄偲婜懸

- TSMC偑師悽戙儘乕僪儅僢僾岞昞丂A13乛A12傪29擭搳擖傊

- DRAM晄懌偱曄傢傞AI僔僗僥儉愝寁丂僄僢僕AI傗摿壔宆儌僨儖偵捛偄晽

- 僜僯乕僙儈僐儞偲TSMC偑崌曎夛幮愝棫傪専摙

- 敿摫懱専嵏憰抲岦偗儗儞僘偺尋杹岺掱偑壱摥丄惗嶻擻椡2.6攞偵

- 26擭3寧偺悽奅敿摫懱巗応偼79亾憹丄擔杮傕10僇寧傇傝僾儔僗惉挿