ISSCC技術講演の2日目午前ハイライト(その1)、強化学習する超小型ロボット、Wi-Fi電波からエネルギーを収穫する回路など:福田昭のデバイス通信(128) 2月開催予定のISSCC 2018をプレビュー(4)(1/2 ページ)

「ISSCC 2018」2日目午前から、注目講演を紹介する。低ジッタのクロック回路技術や、2.4GHz帯のWi-Fi電波からエネルギーを収穫する環境発電回路などについての講演が発表される。

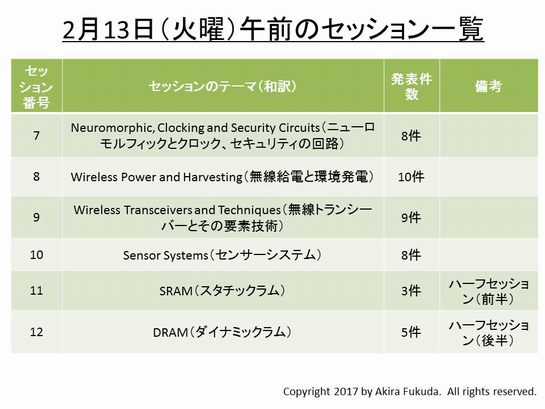

セッション6からセッション12までの6本の技術講演セッションを予定

2018年(来年)2月に米国サンフランシスコで開催予定の半導体回路技術に関する国際学会、「ISSCC 2018」の概要をシリーズでお届けしている。前回は、メインイベントである技術講演セッションの初日午後における技術講演のハイライトをご報告した。今回は2日目午前の技術講演から、ハイライトをご紹介しよう。

2日目である2月13日(火曜日)の午前は、セッション番号だとセッション7からセッション12までの6本のセッションが予定されている。セッション名は「ニューロモルフィックとクロック、セキュリティの回路」(セッション7)、「無線給電と環境発電(エネルギー収穫)」(セッション8)、「無線トランシーバーとその要素技術」(セッション9)、「センサーシステム」(セッション10)、「SRAM」(セッション11)、「DRAM」(セッション12)である。なおセッション11とセッション12は発表件数が少ないハーフセッションで、同じ部屋を使って午前の前半がセッション11、午前の後半がセッション12という進行になる。つまり、全体としては5本の技術講演が同時並行に進む。

超小型ロボットの強化学習をオンラインで実行させる

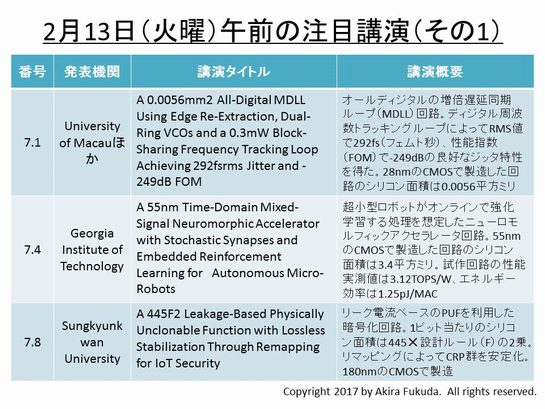

セッション7の「ニューロモルフィックとクロック、セキュリティの回路」は、デジタル回路に関する3つの重要なテーマをカバーしている。クロック、ニューロモルフィック、セキュリティの順番で3件の注目講演をご紹介しよう。

クロック関連では、低ジッタのクロック回路技術に注目したい。中国のUniversity of MacauとポルトガルのUniversity of Lisboaの共同研究チームは、オールデジタルの増倍遅延同期ループ(MDLL:multiplying delayed lock loop)回路を発表する(講演番号7.1)。極めて良好なジッタ特性を達成した。RMS値でのジッタは292フェムト秒、消費電力換算のジッタ(FoM:figure of merit)は−249dBである。28nmのCMOS技術で製造した。回路のシリコン面積は0.0056mm2と小さい。

ニューロモルフィック関連では、オンラインで強化学習を実行可能なアクセラレーター回路が興味深い。Georgia Institute of Technologyは、超小型ロボットがオンラインで強化学習する用途に向けたニューロモルフィックアクセラレータ回路を報告する(講演番号7.4)。55nmのCMOSで製造した回路のシリコン面積は3.4mm2。試作回路の性能実測値は3.12TOPS/W、エネルギー効率は1.25pJ/MAC(積和演算)である。

セキュリティ関連では、個々の半導体チップに特有の信号であるPUF(Physically Unclonable Function)を安定に使うための回路技術に注目したい。韓国のSungkyunkwan University(成均館大学)は、リーク電流をPUFに利用した暗号化回路を発表する(講演番号7.8)。1ビット当たりのシリコン面積は445×(設計ルール(F)の2乗)である。入出力対((チャレンジ・レスポンス・ペア)、(CRP:challenge response pair))群をリマッピングすることでPUFセルを安定化した。試作回路の製造技術は180nmのCMOSである。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- パワー停滞も光デバイス堅調、三菱電機の半導体部門