「RISC-V」はEmbeddedでマーケットシェアを握れるのか:RISC-V Day 2017 Tokyo(5/5 ページ)

Microsemiの講演

写真27:MicrosemiのSenior Technical Director, product architecture and planningのTed Speers氏。氏はまたRISC-V FoundationのBoardも務める

写真27:MicrosemiのSenior Technical Director, product architecture and planningのTed Speers氏。氏はまたRISC-V FoundationのBoardも務める4つ目に御紹介するのがMicrosemiのTed Speers氏(写真27)のセッションである。Microsemiはもともと、旧Actelの流れをくむIGLOO/ProASICシリーズから、そこにAnalog Componentを追加したMixed SignalのSmart Fusion、そして最近新しくミッドレンジ向けにPolarFireシリーズを追加している。

現行製品は6K〜140K LUTという低コスト、低容量かつ小型のIGLOO2と、5K〜150K LUTにCortex-M3コア、それと各種I/F類を大量に装備したSmartFusion 2 SoC FPGA、そして100〜480K LUTと高速SerDesを持つPolarFireというラインアップである。

さて、SmartFusion 2はCortex-M3を搭載しているが、これはHard Coreである。Soft Coreとしては、CoreABC(アセンブラしか無い、非常にシンプルな8bit CPU)、Core8051(8051互換)、Cortex-M1(RTLでの提供のため、一部の製品でしか使えない)がある程度であった。

同社のProduct Catalogをみると他にPIC16互換のDRPIC166Xもラインアップされているが、これはMicroSemiの提供ではなく、ポーランドのDCD(Digital Core Design)が提供するものに見える。いずれにせよXilinxのMicroBlaze/PicoBlazeとかAltera(現Intel)のNIOS II、LatticeのMico32などに比べるとやや見劣りしていると判断したためだろうか、同社は2016年に早くもRISC-VをSoft Coreとして提供すると発表している(関連記事:「Microsemi、FPGA向けのRISC-V IPコアを提供へ」)。

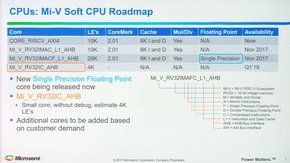

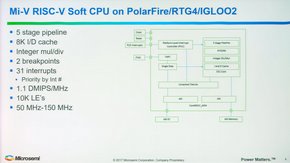

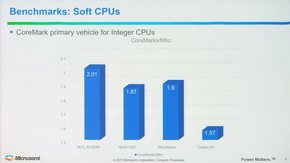

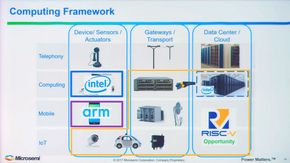

そのMicrosemi、最初に提供されたCORE_RISCV_AXI4に続き、Mi_V_RV32IMACシリーズを2017年11月に提供しており、間もなくMi_V_RV32IC_AHBの提供が予定されている(写真28)。当初の製品は10〜26K LUTを占有していて、PolarFireにはともかくIGLOO 2にはちょっと大きいものだったが、新しいMi_V_RV32IC_AHBだと4K LUTで実装できるから、IGLOO 2クラスでも安心して利用できる事になる。ベースがSiFiveのE31だから、SiFiveのE31と同程度の性能/MHzは期待できるし、E31用のOSとかミドルウェア、開発環境もほぼそのまま利用できるのが大きなメリットで、この時点で他の競合Soft Coreに比べて大きなアドバンテージを得た形だ(写真29)。同社によれば性能も良好(写真30)とする。もっとも、MicrosemiによるMarketing Target(写真31)は、ちょっと風呂敷を広げすぎという気もしなくはないが。

左=写真28:ちなみに最初の3つのコアの実体はSiFiveのE31コアそのものである/右=写真29:最初の3つのコアの構成。Mi-V_RV32IMACF_L1_AHBはこれにSingle PrecisionのFPUが追加される事になる(クリックで拡大)

左=写真28:ちなみに最初の3つのコアの実体はSiFiveのE31コアそのものである/右=写真29:最初の3つのコアの構成。Mi-V_RV32IMACF_L1_AHBはこれにSingle PrecisionのFPUが追加される事になる(クリックで拡大)

左=写真30:まぁSoft Coreで2 CoreMark/MHz出れば大したものだという気はする/右=写真31:ArmをMobileのみに押し込めておくのはちょっと無理が無いだろうか?(クリックで拡大)

左=写真30:まぁSoft Coreで2 CoreMark/MHz出れば大したものだという気はする/右=写真31:ArmをMobileのみに押し込めておくのはちょっと無理が無いだろうか?(クリックで拡大)ということで4つのセッションの内容をお届けしたところで、ちょっと筆者なりの分析というか感想を付け加えたいと思う。再び写真6に戻るが、現在のSoC内部に搭載される多様多種なコントローラーをRISC-Vでまとめることができるか? というと、「いろいろ足りてないんじゃ?」というのが率直な意見である。

現在のRISC-Vは、Minimum TargetをArmのCortex-M3とかM4に置いており、ISA自身もこの辺りを実現するのがMinimum Requirementと踏んでいる節が見受けられる。ところが実際には、特にSoCに含まれるコントローラーの場合、写真6にもあるようにDSPだったり、32bit未満のMCUだったり、あるいはVLIWタイプのアクセラレータだったりする。こうしたものを置き換えるには、RISC-VのISAはやや汎用の高性能向けに振れ過ぎている(もっと正確に言えば、Base Specificationがちょっと高機能より過ぎる)ように思われる。

例えばDSPについてはAndesがDSP Extentionを大幅に強化した事を写真19で紹介しているが、逆にAudio DSPとかRadio DSPの場合このDSP Extentionとごく少数のBase Specificationの命令(Load/Storeと若干の制御命令)だけあれば良いように思う。あるいはDSPでもSIMDではなくVLIWタイプの実装だと、そもそもRISC-VのISAと相いれない(現在はCadenceに買収された、TensilicaのXtensaがこのタイプ)。

また、今でも8〜16bitのMCUが依然として結構な割合を占めているのも事実である。特にSoCの内部のIPで使われるようなものでは、ダイのエリアサイズをぎりぎりまで詰めるために、8bit MCU IPが依然多く使われている。RISC-Vの圧縮命令でこれが代替できるか? といわれると、ちょっと厳しいように見える。こうした用途向けだともちろんMacro Fusionの機能などはコアに搭載されないから、圧縮命令を使ってもまだコード密度は従来の8bit MCUより落ちるだろうし、それをカバーするために大きめのProgram Storage Area(EEPROMになるのかOTPになるのかFlashになるのかはケースバイケース)を必要とするのは、果たして受け入れられるだろうか? と首を傾げざるを得ない。よくArmが"One size doesn't fit all"を口にする(彼らの意味は「1種類のコアで全てのマーケットに対応させるのは無理」)が、RISC-Vもこうした組み込みのローエンドにはちょっとFitしないんじゃないか? という気がする。

その一方でもう少し上のレベル、それこそCortex-M3以上のレベルでは、なかなか悪くないFeatureと、特に中国などでは魅力的なライセンス形態になっている。特にちょっとしたコントローラー向けで、従来だとx86とかArmのCortex-A5/A7/A9などを使っていた用途の代替には、特にライセンス料の関係で今後入ってゆく可能性があるだろう。

結果として、まず従来のMIPSあるいはPowerPCベースの製品マーケットと、一部ArmのCortex-Aのマーケットを侵食してゆく可能性が高いと思う。Cortex-Mについては難しいが、例えば今回は名前が挙がっていないものの、RISC-V Foundationに加盟しているフランスのCortusは、既にAPS3VというRV32IベースのIPの提供を開始している。5〜7ステージのパイプラインと、わずか8642ゲート(+レジスタファイル)という小ささは、Cortex-M0に匹敵するレベルである。Armのエコシステムに乗る必要の無いユーザーにとって、これはなかなか魅力的なスペックである。なので、Armである必要はないがMCUは必要、という(今となってはややニッチな)ニーズが増えるようであれば、可能性は低くないだろう。

RISC-Vの次の課題はセキュリティであろうかと思う。ArmのTrustZoneとか、最近MCU向けに提供を開始したPSAにあたるものを、現在のISAのスキームのまま(命令拡張だけで)実装できるのか、あるいはBase Instructionの変更が必要なのか。この辺りをまずは注視したいと思う。

関連記事

関心高まるRISC-V、Armやx86の代替となり得るか

関心高まるRISC-V、Armやx86の代替となり得るか

2017年11月28〜30日にかけて、米国シリコンバレーで「7th RISC-V Workshop」が開催された。オープンな命令セットアーキテクチャ「RISC-V」は、Arm系やx86系の命令セットの代替となり得る技術として確実に台頭してきている。 Microsemi、FPGA向けのRISC-V IPコアを提供へ

Microsemi、FPGA向けのRISC-V IPコアを提供へ

Microsemi(マイクロセミ)が、同社のFPGA「IGLOO2」「RTG4」やSoC FPGA「SmartFusion」などに向けた、RISC-VのソフトウェアIPコアを発表した。 RISC-Vベースチップ手掛ける新興企業が資金調達

RISC-Vベースチップ手掛ける新興企業が資金調達

RISC-VアーキテクチャをベースのCPUコアやカスタムSoCなどを手掛ける米国の新興企業SiFiveが合計1350万米ドルの資金を調達した。 デンソーの新子会社とプロセッサを開発するThinCIとは

デンソーの新子会社とプロセッサを開発するThinCIとは

デンソーが新設する子会社「エヌエスアイテクス(NSITEXE)」とプロセッサを共同開発するのが、米新興企業のThinCIだ。同社のCEO(最高経営責任者)を務めるDinakar Munagala氏に、同社の製品の強みなどを聞いた。 ルネサス、セキュリティ強化したIIoT用MCU

ルネサス、セキュリティ強化したIIoT用MCU

ルネサス エレクトロニクスは2017年11月13日、産業用IoT(モノのインターネット)機器向けの32ビットマイコンとして、セキュリティ機能を強化した「RX65N/RX651グループ」のサンプル出荷を開始した。 MCUにIC1つ加えるだけのセキュリティ対策を提案

MCUにIC1つ加えるだけのセキュリティ対策を提案

Maxim Integrated Products(マキシム・インテグレーテッド・プロダクツ)は、一般的なマイコンとともに使用することで、組み込み機器に必要とされる各種セキュリティ機能を実現できる暗号コントローラーICの提案を展開している。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 加賀電子が新光商事にTOB、完全子会社化へ

- SiC LSIの事業化に挑む 28年以降ADCのサンプル出荷へ

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- Cerebrasが上場 NVIDIA対抗馬の「試金石」となるか

- AIの「トンデモ判断」で本番DBが全飛び! 他山の石にしたいAIコーディングの落とし穴

- サンケン電気26年3月期は赤字転落 中国の「自前主義」響く

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略