技術講演の最終日午前(その3)、72Gサンプル/秒の8ビット超高速A-D変換回路:福田昭のデバイス通信(134) 2月開催予定のISSCC 2018をプレビュー(10)(1/2 ページ)

「ISSCC 2018」最終日午前の技術講演から、セッション21と22を紹介する。データ転送速度が10Gビット/秒で消費電力が150μWのシリコンフォトニクス送受信回路や、72Gサンプル/秒の8ビットSAR型A-D変換回路などについて、開発成果が披露される。

近未来をにらんだ半導体チップと超高速データ変換チップ

2018年(今年)2月に米国サンフランシスコで開催予定の国際学会「ISSCC 2018」の概要をシリーズでお届けしている。前回は、メインイベントである技術講演セッションの最終日午前(現地時間で2月14日水曜日午前8時30分開始予定)から、セッション19(センサーとインタフェース)とセッション20(フラッシュメモリ)のハイライトをお届けした。今回は、同じ最終日午前のハイライトを続けてご紹介する。

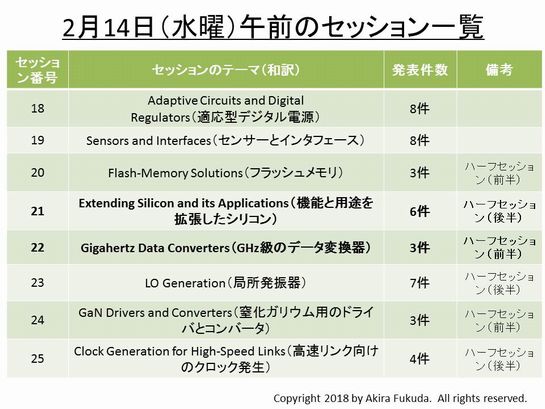

繰り返しになるが、最終日の午前にはセッション18〜セッション25の8本のセッションが予定されている。その中でセッション20〜セッション25の5本はハーフセッション(同じ部屋を前半と後半の時間に分けて使うセッション)である。全体としては5本のセッションが同時並行で進行する。

セッション名は番号順に、「適応型デジタル電源」(セッション18)、「センサーとインタフェース」(セッション19)、「フラッシュメモリ」(セッション20)、「機能と用途を拡張したシリコン」(セッション21)、「GHz級のデータ変換器」(セッション22)、「局所発振器」(セッション23)、「窒化ガリウム用のドライバとコンバーター」(セッション24)、「高速リンク向けのクロック発生」(セッション25)となっている。その中から、今回はセッション21とセッション22のハイライトをご紹介しよう。

アナログ信号を非線形にデジタル信号に変換

セッション21の「機能と用途を拡張したシリコン」は、近未来に向けた特定用途向け半導体チップの研究成果を披露するセッションである。

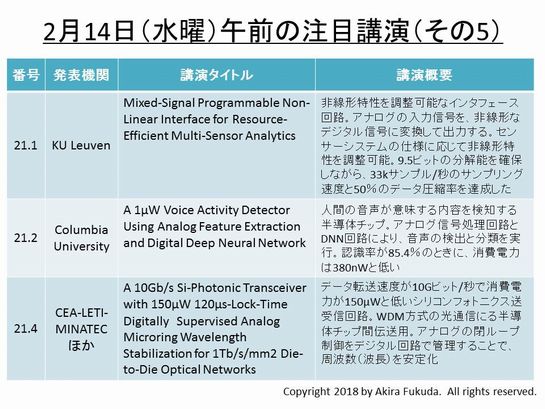

ベルギーのKU Leuven(ルーベン工科大学)は、非線形特性を調整可能なミックスドシグナル・インタフェース回路を発表する(講演番号21.1)。センサーシステムでの利用を想定した。アナログの入力信号を、非線形なデジタル信号に変換して出力する。センサーシステムの仕様に応じて非線形特性を調整可能なことが特徴。9.5ビットの分解能を確保しながら、33kサンプル/秒のサンプリング速度と50%のデータ圧縮率を達成した。製造技術は90nmのCMOSプロセス。

Columbia Universityは、人間の音声が意味する内容を検知する低消費電力の半導体チップを報告する(講演番号21.2)。音声によって動作を指示可能なモバイル機器やウェアラブル機器などに向けた。アナログ信号処理回路と深層ニューラルネットワーク(DNN: Deep Neural Network)回路により、音声の検出と分類を実行する。認識率が85.4%のときに、消費電力は380nWと低い。

フランスのCEA-LETI-MINATECとフランスのSTMicroelectronicsによる共同研究グループは、データ転送速度が10Gビット/秒で消費電力が150μWと低いシリコンフォトニクス送受信回路を発表する(講演番号21.4)。波長分割多重(WDM: Wavelength Division Multiplexing)方式の光通信によって半導体チップ間で信号をやりとりする用途に向けた。アナログの閉ループ制御をデジタル回路で管理することで、周波数(波長)を安定化する。周波数をロックするまでの所要時間は120マイクロ秒である。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 加賀電子が新光商事にTOB、完全子会社化へ

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

- SiC LSIの事業化に挑む 28年以降ADCのサンプル出荷へ

- AIの「トンデモ判断」で本番DBが全飛び! 他山の石にしたいAIコーディングの落とし穴

- サンケン電気26年3月期は赤字転落 中国の「自前主義」響く

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk