技術講演の最終日午前(その3)、72Gサンプル/秒の8ビット超高速A-D変換回路:福田昭のデバイス通信(134) 2月開催予定のISSCC 2018をプレビュー(10)(2/2 ページ)

16ビットで12Gサンプル/秒の高分解能高速D-A変換技術

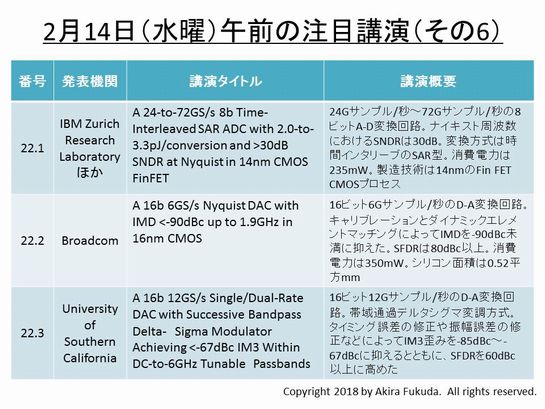

セッション22の「GHz級のデータ変換器」では、超高速のアナログデジタル変換(A-D変換)技術とデジタルアナログ変換(D-A変換)技術が披露される。

スイスのIBM Zurich Research LaboratoryとスイスのETH Zurich(チューリッヒ工科大学)、スイスのEPFL(スイス連邦工科大学ローザンヌ校)の共同研究グループは、サンプリング速度が24Gサンプル/秒〜72Gサンプル/秒と極めて高い8ビットのA-D変換回路を発表する(講演番号22.1)。ナイキスト周波数におけるSNDR(Signal-to-Noise and Distortion Ratio)は30dB。変換方式は時間インタリーブの逐次比較レジスタ(SAR: Successive Approximation Register)型である。階層構造の16並列サンプリングスイッチをインタリーブ動作させる。1個のサンプリングスイッチに4個のサブA-D変換回路を接続した。消費電力は235mW。製造技術は14nmのFinFET CMOSプロセスである。

ミックスドシグナル半導体大手のBroadcomは、分解能が16ビットと高く、変換速度が6Gサンプル/秒と高速のD-A変換回路を開発した(講演番号22.2)。ナイキストサンプリング方式。キャリブレーションとダイナミックエレメントマッチングによって混変調歪み(IMD: Inter-Moulation Distortion)を−90dBc未満に抑えた(周波数範囲は1.9GHz)。SFDR(Spurious-Free Dynamic Range)は80dBc以上(周波数範囲は900MHz)である。消費電力は350mW。シリコン面積は0.52mm2。製造技術は16nmのCMOSプロセスである。

University of Southern Californiaは、分解能が16ビットと高く、変換速度が12Gサンプル/秒と高速のD-A変換回路を発表する(講演番号22.3)。オーバーサンプリング(帯域通過デルタシグマ変調)方式。タイミング誤差の修正機能と振幅誤差の修正機能、逆SINCプリディストーションによって3次相互変調(IM3: Inter. Modulation 3)歪みを−85dBc〜−67dBc(ナイキスト周波数までの領域)に抑えるとともに、SFDRを60dBc以上(周波数は4.2GHz)に高めた。製造技術は65nmのCMOSプロセスである。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

ISSCC技術講演の2日目午後ハイライト(その2)、低ジッタの高周波PLL、全天周撮影のカプセル内視鏡など

ISSCC技術講演の2日目午後ハイライト(その2)、低ジッタの高周波PLL、全天周撮影のカプセル内視鏡など

前回に続き、「ISSCC 2018」2日目午後の技術講演から、見どころを紹介する。低消費電力の2.4GHz帯無線端末用PLL回路や、全天周をVGA解像度で撮影するカプセル内視鏡などが登場する。 ISSCC技術講演の2日目午前ハイライト(その2)、GPS不要の超小型ナビ、16Gビット高速大容量DRAMなど

ISSCC技術講演の2日目午前ハイライト(その2)、GPS不要の超小型ナビ、16Gビット高速大容量DRAMなど

「ISSCC 2018」2日目午前に行われるセッションのうち、セッション9〜12の見どころを紹介する。76GHz〜81GHz帯を使用する車載用ミリ波レーダー送受信回路や、超小型の慣性式ナビゲーションシステム、GDDR6準拠の16GビットDRAMなどが登場する。 ISSCC技術講演の2日目午前ハイライト(その1)、強化学習する超小型ロボット、Wi-Fi電波からエネルギーを収穫する回路など

ISSCC技術講演の2日目午前ハイライト(その1)、強化学習する超小型ロボット、Wi-Fi電波からエネルギーを収穫する回路など

「ISSCC 2018」2日目午前から、注目講演を紹介する。低ジッタのクロック回路技術や、2.4GHz帯のWi-Fi電波からエネルギーを収穫する環境発電回路などについての講演が発表される。 “ハイブリッド構成”の降圧DC-DCコントローラー

“ハイブリッド構成”の降圧DC-DCコントローラー

Analog Devices(ADI)は、入力電圧範囲が10〜72VのDC-DCコントローラー「LTC7821」を発表した。スイッチドキャパシター回路と同期整流式降圧DC-DCコントローラー回路を組み合わせ、1チップにした製品で、従来に比べて実装面積を最大50%低減できる。 車載レーダーの限界はアナログへの回帰で超える

車載レーダーの限界はアナログへの回帰で超える

米スタートアップのMetawaveは、車載レーダー技術を手掛けている。既存の車載レーダーの性能の限界を超える鍵は、アナログビームフォーミング技術だという。 車載向けオペアンプ、ノイズ設計フリーを実現

車載向けオペアンプ、ノイズ設計フリーを実現

ロームは、「オートモーティブ ワールド 2018」で、未来のクルマの「安全」「快適」「環境」を実現するためのSiCパワーデバイスやオペアンプIC、オーディオシステム向けソリューションなどを紹介した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 加賀電子が新光商事にTOB、完全子会社化へ

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

- SiC LSIの事業化に挑む 28年以降ADCのサンプル出荷へ

- AIの「トンデモ判断」で本番DBが全飛び! 他山の石にしたいAIコーディングの落とし穴

- サンケン電気26年3月期は赤字転落 中国の「自前主義」響く

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk