畳み込みをアナログで、エッジでも推論できるチップ:アナログ積和演算で高効率

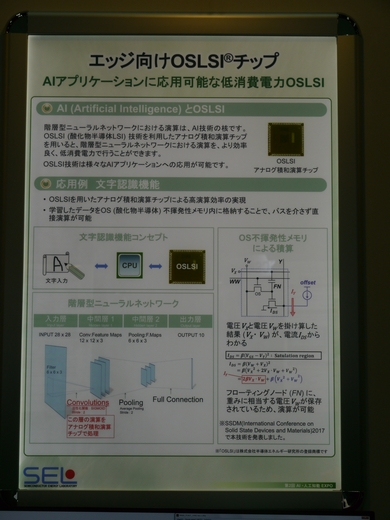

半導体エネルギー研究所は、「第2回 AI・人工知能 EXPO」で、同社が開発を進める酸化物半導体LSI「OSLSI」を活用したAI(人工知能)チップを紹介した。エッジデバイス上でニューラルネットワークを高効率、低消費電力に実行可能だとする。

多数のアナログ積和演算器で畳み込み演算を実行

半導体エネルギー研究所は、「第2回 AI・人工知能 EXPO」(2018年4月4日〜6日、東京ビッグサイト)で、酸化物半導体を活用したAI(人工知能)チップを紹介した。同チップではアナログで積和演算を実行し、エッジデバイス上で階層型ニューラルネットワークによる推論を高効率、低消費電力に実現するという。

同社は、結晶性酸化物半導体(CAAC-IGZO)を用いたFET「OSFET」の研究を行っており、メモリやCPUなどOSFETを利用したさまざまな電子デバイス「OSLSI」への応用を進める。OSFETは、シリコンを用いた通常のFET(Si FET)と比較して大幅に低いオフ電流特性を有し、さらにSi FET上にOSFET回路を積層可能なことが特長となる。

OSFETをメモリに応用した一例として、DRAMメモリセルのトランジスタをOSFETに置き換えた「DOSRAM」が挙げられる。DOSRAMではOSFETの低オフ電流特性を生かして、リフレッシュ動作を1時間から年に数回程度まで削減できる。また、DRAMではメモリセルとセンスアンプが平面的に配置されているため長い配線を確保する必要があるが、DOSRAMではメモリセルとセンスアンプを積層することにより配線長を削減し低消費電力動作を実現するという。

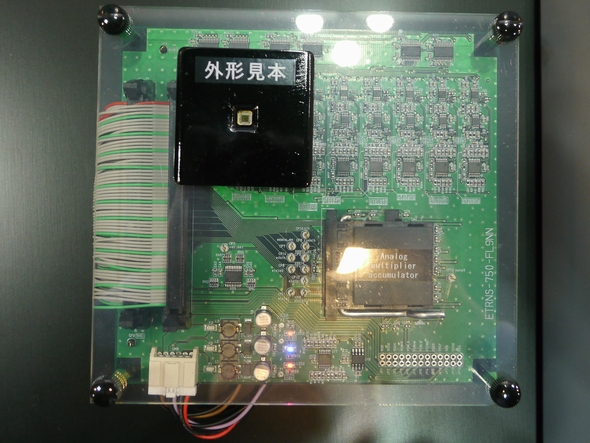

今回展示されたAIチップは複数のOSLSIで構成され、その演算部となる「osMemory Logic」はアナログで積和演算を行っている。osMemory Logicは、Si FET上にOSFETを積層した2個のトランジスタと1個のキャパシターの構造となっており、オンサイトメモリと乗算回路を兼ねる。

積和演算には2素子のosMemory Logicを使用し、それぞれの素子の入力電圧と重み係数に対応した電流が流れることで計算を行う。デジタル積和演算回路と比較して小規模な回路実装となることがメリットだ。このosMemory Logicを並列実装することで、階層型ニューラルネットワークの畳み込み演算を、高速かつ低消費電力、省スペースで実現できるという。

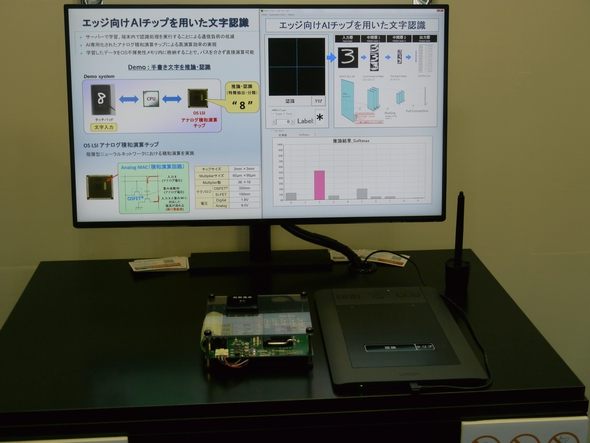

同社ブースではこのチップを用いて、ペンタブレットで数字を書くと同チップが推論を行い、数秒後に書いた数字が判定されるというデモを展示。デモで用いられたチップは、3×3mmサイズで36×16個のosMemory Logicを搭載し、OSFETが350nm、Si FETが150nmのプロセスルールで製造された。同社担当者によると「50〜60nmプロセスルールの対応は既にできている」とする。

今回展示されたAIチップの具体的な市場投入時期は未定。一方、共同研究先である台湾の半導体ファウンドリーUMCで酸化物半導体の製造ラインを構築するとしており、担当者は「2019年中に製造ラインを立ち上げ、メモリから商用化を始める予定」としている。

関連記事

自動運転ベンチャーが独自のCNN IPコアを開発した理由

自動運転ベンチャーが独自のCNN IPコアを開発した理由

菱洋エレクトロと自動運転ベンチャーの「AImotive(エーアイモーティブ)」は、AImotiveが開発した独自IP(Intellectual Property)による畳み込みニューラルネットワーク(CNN:Convolutional Neural Network)アクセラレーター「aiWare」と、同社の自動運転ソフトウェア「aiDrive」を搭載したデモ車両を日本で初披露した。 AI発展のため、脳の研究に立ち返る科学者たち

AI発展のため、脳の研究に立ち返る科学者たち

AI(人工知能)の研究開発を進めるに当たり、研究者たちは「脳の機能を理解する」という原点に立ち返っているようだ。研究がより進めば、AIの性能もそれだけ向上するのではないかと期待されている。 「AIとはソフトの進化」 Intelが取り組みを強化

「AIとはソフトの進化」 Intelが取り組みを強化

Intelは2017年12月5日に東京都内で記者説明会を開催。2017年における同社の取り組みを振り返った。AI(人工知能)分野については、京都大学医学部の専門家が登壇し、Intelのプロセッサを使った機械学習のシステムを、創薬に導入した事例を語った。 ArmのAI戦略、見え始めたシナリオ

ArmのAI戦略、見え始めたシナリオ

機械学習についてなかなか動きを見せなかったArmだが、モバイルやエッジデバイスで機械学習を利用する機運が高まっているという背景を受け、少しずつ戦略のシナリオを見せ始めている。 AI性能20倍、Xilinxが7nm世代製品「ACAP」発表

AI性能20倍、Xilinxが7nm世代製品「ACAP」発表

Xilinxは2018年3月19日(米国時間)、7nmプロセスを用いる新たな製品群「ACAP」(エーキャップ)を発表した。新たなプログラマブル演算エンジンなどを搭載し、現行のFPGA製品よりも20倍高いAI(人工知能)演算性能を発揮するという。 GoogleからAI用プロセッサ「TPU」が登場

GoogleからAI用プロセッサ「TPU」が登場

Googleが、人工知能(AI)に向けたアクセラレータチップ「Tensor Processing Unit(TPU)」を独自開発したことを明らかにした。同社が2015年にリリースした、オープンソースのアルゴリズム「TensorFlow」に対応するという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング