AI性能20倍、Xilinxが7nm世代製品「ACAP」発表:2019年に出荷へ

Xilinxは2018年3月19日(米国時間)、7nmプロセスを用いる新たな製品群「ACAP」(エーキャップ)を発表した。新たなプログラマブル演算エンジンなどを搭載し、現行のFPGA製品よりも20倍高いAI(人工知能)演算性能を発揮するという。

HW/SWプログラマブルエンジン

Xilinxは2018年3月19日(米国時間)、7nmプロセスを用いる新たな製品群「ACAP」(エーキャップ)を発表した。プログラマブルロジック、複数種のプロセッサコアなどとともに、ビデオ処理やAI(人工知能)推論などの処理に適したプログラマブルな演算エンジン「HW/SWプログラマブルエンジン」と搭載するデバイス製品。Xilinxは、ACAPのAI演算性能は現行の16nmプロセス採用ハイエンドFPGA製品(Virtex VU9P)に比べ20倍に達するという。2018年中に設計開発を完了させ、2019年に製品出荷を開始する予定。

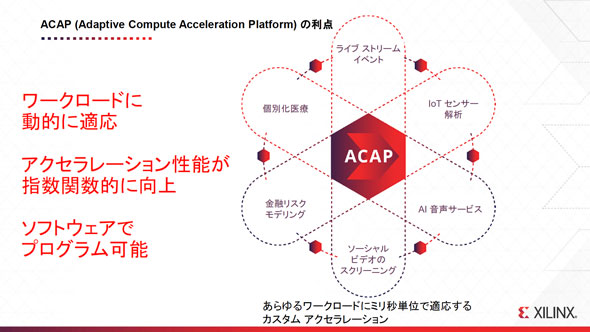

Xilinxは、今回発表したACAPを「従来FPGAの性能をはるかにしのぐ、全く新しい製品カテゴリー」と位置付ける。ACAPは、Adaptive Compute Acceleration Platform(=適応型演算プラットフォーム)の略で、開発コード名はEverest(エベレスト)。

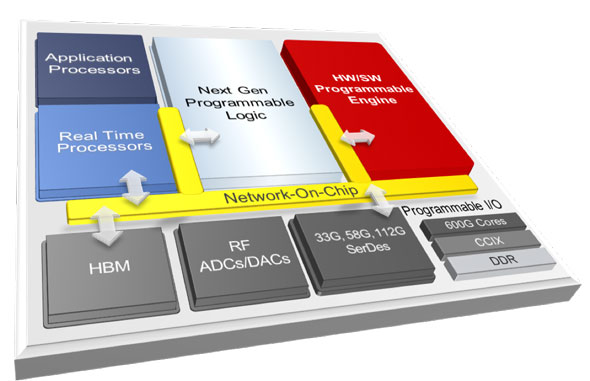

ACAPの構成要素は、次世代プログラマブルロジックと、アプリケーションプロセッサ、リアルタイムプロセッサ、HBM、RF・A-D/D-Aコンバーター、最高112Gビット/秒対応のSerDes、プログラマブルI/Oなどであり、Xilinxが展開するFPGAにCPUコアを搭載しプログラマブルSoC(System on Chip)と位置付ける「Zynq」に似る。ACAPがZynqと異なる製品カテゴリーに位置付ける理由は、ACAPが動的に構成を変更できる演算エンジン「HW/SWプログラマブルエンジン」を搭載する点。「このHW/SWプログラマブルエンジンがACAPの最大の特長」(Xilinx 社長兼CEOのVictor Peng氏)という。

「ACAP」のデバイス内部構成。新たにHW/SWプログラマブルエンジンを搭載した他、ネットワークオンチップ対応となった。なお、トランジスタ搭載数は500億個規模になる見込み (クリックで拡大) 出典:Xilinx

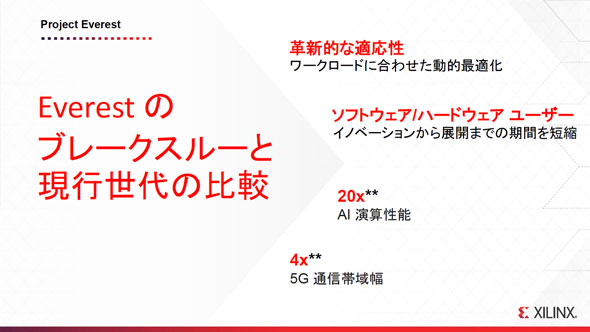

「ACAP」のデバイス内部構成。新たにHW/SWプログラマブルエンジンを搭載した他、ネットワークオンチップ対応となった。なお、トランジスタ搭載数は500億個規模になる見込み (クリックで拡大) 出典:XilinxHW/SWプログラマブルエンジンは、処理負荷に応じてその構成をミリ秒単位で動的に最適化できるとし、ビデオの圧縮符号化、データ圧縮、検索、AI推論、ゲノミクス、マシンビジョンなどの幅広い用途のアクセラレーションで、その性能を発揮するという。16nm世代FPGA(Virtex VU9P)に比べ、ディープニューラルネットワークを実装した場合、20倍の性能向上が期待できるとする。また、第5世代移動通信(5G)のリモートラジオヘッドでは、16nm世代FPGAに比べ4倍の帯域幅に対応できるとする。Peng氏は「1W当たりの性能も、16nm世代FPGAの10倍以上になる」と高い電力効率を実現できるとの見通しを示した。

適応性のあるアクセラレーテッドコンピューティング

2018年1月に社長兼CEOに就任したPeng氏は、Xilinxを取り巻く市場のトレンドとして「データの爆発的増加」「AI時代の到来」「ムーアの法則後のコンピューティング」の3つを挙げ、それらのトレンドに対応するには「適応性のあるアクセラレーテッドコンピューティングが必要」とする。ACAPは、そうした“適応性のあるアクセラレーテッドコンピューティング”の提供を目指す新体制下のXilinxを象徴するデバイスになる。Peng氏は「ACAPの開発に、4年の年月を費やし、1500人のエンジニアが関わり、10億米ドル以上の研究開発費を投じている」としている。

ACAPは、TSMCの7nmプロセスラインで製造を行う方針で、Xilinxとして最初の7nmプロセス採用製品となる。既に一部の顧客に対しては、ソフトウェアツール(アーリーアクセス版)の提供を開始している。

関連記事

7nmプロセスの開発が加速、EUVの導入も現実的に

7nmプロセスの開発が加速、EUVの導入も現実的に

ファウンドリー各社が7nmプロセスの開発を加速している。さらに、半導体製造装置メーカーのASMLもEUV(極端紫外線)リソグラフィシステムの開発を順調に進めている。 Qualcomm、5G対応SnapdragonにSamsungの7nm EUVを適用

Qualcomm、5G対応SnapdragonにSamsungの7nm EUVを適用

Qualcommは2018年2月、同社の5G(第5世代移動通信)チップセット「Snapdragon」に、Samsung ElectronicsのEUV(極端紫外線)リソグラフィを導入した7nm LPP(Low Power Plus)プロセス技術を適用することを発表した。 Xilinx、FPGA/SoCからソフト企業へ

Xilinx、FPGA/SoCからソフト企業へ

Xilinx(ザイリンクス)は、東京都内で「ザイリンクス開発者フォーラム 2017(XDF 2017)」を開催。クラウドベースアプリケーションのFPGA開発にフォーカスし、その効果や開発ツールの最新動向などを紹介した。 Xilinx、ASIL-C準拠のZynq UltraScale+MPSoC

Xilinx、ASIL-C準拠のZynq UltraScale+MPSoC

Xilinxは、オートモーティブ事業において、ADAS(先進運転支援システム)や自動運転システムに向けた製品展開を強化する。新たにASIL-C準拠の「XA Zynq UltraScale+MPSoC」を市場に投入した。 TSMC、7nm/EUVの開発状況をアップデート

TSMC、7nm/EUVの開発状況をアップデート

TSMCは2017年9月、米国で開催されたイベントで7nmプロセス技術やEUV(極端紫外線)リソグラフィの開発状況などを説明した。 エッジコンピューティング、低電力でAI実現

エッジコンピューティング、低電力でAI実現

AI(人工知能)技術をベースとしたエッジコンピューティングを次の成長ドライバーと位置付けるLattice Semiconductor。フォーカスする分野は消費電力が1W以下で、処理性能は1テラOPS(Operations Per Second)までのアプリケーションだ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

「ACAP」(開発コード名:Everest)の特長と従来品との性能比較 出典:Xilinx

「ACAP」(開発コード名:Everest)の特長と従来品との性能比較 出典:Xilinx