シリコンフォトニクスとは何か:福田昭のデバイス通信(143) imecが語る最新のシリコンフォトニクス技術(3)(1/2 ページ)

今回は、「シリコンフォトニクス」技術を紹介する。そもそも「シリコンフォトニクス」とは何か、そしてその利点と課題について解説したい。

シリコンCMOS集積回路の製造インフラで光デバイスを作る

半導体デバイス技術に関する国際会議「IEDM」では、カンファレンスの前々日に「チュートリアル(Tutorial)」と呼ぶ技術セミナーを開催している。2017年12月に開催されたIEDMでは、6件のチュートリアルが開催された。

その中から、シリコンフォトニクスに関する講座「Silicon Photonics for Next-Generation Optical Interconnects(次世代光接続に向けたシリコンフォトニクス)」が興味深かったので、その概要をシリーズでお届けしている。講演者は、ベルギーの研究開発機関imecのJoris Van Campenhout氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前回は、データセンターにおける光通信と電気通信の進化と境界についてご報告した。今回は次世代の光通信を担うと期待される「シリコンフォトニクス」技術の概要と、その将来性を解説する。

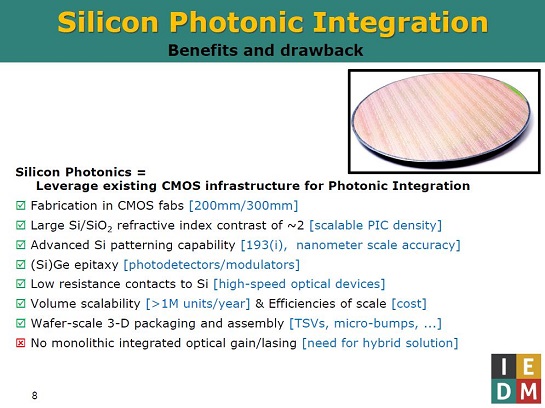

始めに「シリコンフォトニクス(Slicon Photonics)」とは何かについて説明しよう。一言でまとめると、「シリコンCMOS集積回路の製造インフラストラクチャ(シリコンの製造インフラ)を利用して光デバイスを集積し、製造すること」となる。

シリコンの製造インフラとは、CMOSの大規模集積回路と同様に、直径が200mmあるいは300mmのシリコンウエハーを使うプロセス技術で製造することを意味する。前回に説明したように、光集積回路のほぼ全ての機能はInP基板の上に作製できる。ただしInP基板(ウエハー)には、最大でも直径が150mmと小さい、高密度の結晶欠陥(転位欠陥)が存在する、ウエハーの価格が高い、といった課題がある。光集積回路を低コストで量産するためには、大口径かつ安価で無欠陥のシリコンウエハーを基板とすることが望ましい。

このほかにもシリコンの製造インフラを使えるメリットは少なくない。CMOSロジックの最先端微細加工技術が利用できるので、原理的には光デバイスを微細化できる。CMOSの高密度な電子回路を光回路と一体化して作れる。CMOSデバイス向けの高密度なパッケージング技術(例えばウエハーレベルパッケージング技術)を利用可能になる。これらのメリットが期待できる。

光集積回路を構成するためには、各種の光デバイスを作製しなければならない。光導波路(光ファイバーのような伝送路を半導体基板あるいは絶縁基板に形成したもの)と受光素子、光変調素子はシリコン基板で比較的簡単に作れる。

もちろん課題はある。最大の問題は、シリコン材料では半導体レーザー(発光素子)を作れないことだろう。今のところ、半導体レーザーはInP基板で作らざるを得ない。InP基板で作製した半導体レーザーのダイ(微小なチップ)を、シリコンダイと接続する技術が必要となる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待