多層配線工程に記憶素子を埋め込む不揮発性メモリ技術(前編):福田昭のストレージ通信(99)STが語る車載用埋め込み不揮発性メモリ(12)(1/2 ページ)

多層配線工程の中に記憶素子を作り込むタイプの埋め込み不揮発性メモリ技術について解説する。

CMOSロジックの微細化に追随できない埋め込みフラッシュ

国際会議「IEDM」の「ショートコース(Short Course)」から、車載用の埋め込み不揮発性メモリに関する講座「Embedded Non Volatile Memories for Automotive Applications」の概要をご紹介している。講演者は半導体ベンダーSTMicroelectronics(STマイクロエレクトロニクス)のAlfonso Maurelli氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前回は、これまで述べてきた車載用埋め込みフラッシュメモリ技術を総括した。今回は、多層配線工程の中に記憶素子を作り込むタイプの埋め込み不揮発性メモリ技術をご紹介する。

前回で述べたように、埋め込みフラッシュメモリの微細加工技術はCMOSロジックに比べ、2世代以上、時期としては3年〜5年ほど、遅れてきた。しかも最近では、遅れがさらにひどくなりつつある。40nm技術、あるいは28nm技術で埋め込みフラッシュメモリの微細化が停滞しつつあるからだ。フラッシュメモリの記憶原理には浮遊ゲート型と電荷捕獲型がある。特に浮遊ゲート型では、ロジック用MOSFETの微細化に追随することが困難になってきた。

埋め込みフラッシュメモリは基本的に、独自構造のセルトランジスタによってデータを記憶している。セルトランジスタは、CMOSロジックとは製造プロセスの互換性をなるべく維持する必要がある。このため、ロジック用MOSFETの構造が微細化によって大きく変化すると、フラッシュメモリのセルトランジスタの構造も併せて変えないと、微細化に追従できない。

最近の最先端ロジック用トランジスタにおける特に大きな構造変化は、FinFET(フィン状のチャンネルを備えたFET)が使われるようになったことだ。16nm/14nm世代以降のロジック用トランジスタは、FinFETが主流である。浮遊ゲート方式のフラッシュメモリはセルトランジスタのゲートが積層構造であるため、フィン構造と積層ゲートの両立が原理的にかなり難しい。

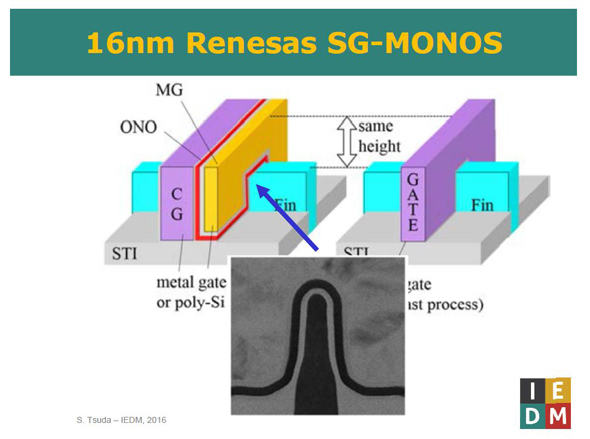

一方、電荷捕獲型のフラッシュメモリは、技術的な可能性が見えている。電荷捕獲型の埋め込みフラッシュメモリ技術「SG-MONOS」を開発してきたルネサス エレクトロニクスは、16nm世代のFinFETプロセスと互換性のあるSG-MONOS技術を、国際学会で発表済みである。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増