シリコンフォトニクスの技術開発ロードマップ:福田昭のデバイス通信(144) imecが語る最新のシリコンフォトニクス技術(4)(1/2 ページ)

今回は、シリコンフォトニクスの技術開発ロードマップを解説する。シリコンフォトニクスの性能向上とコストを、16/14nmから5nm、3nmの技術ノードに沿って見ていこう。

CMOS技術ノードの進化とともに、シリコンフォトニクスが進化

半導体デバイス技術に関する国際会議「IEDM」では、カンファレンスの前々日に「チュートリアル(Tutorial)」と呼ぶ技術セミナーを開催している。2017年12月に開催されたIEDMでは、6件のチュートリアルが開催された。

その中から、シリコンフォトニクスに関する講座「Silicon Photonics for Next-Generation Optical Interconnects(次世代光接続に向けたシリコンフォトニクス)」が興味深かったので、その概要をシリーズでお届けしている。講演者は、ベルギーの研究開発機関imecのJoris Van Campenhout氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前回は、本題である「シリコンフォトニクス」とは何かを説明した。今回は、シリコンフォトニクスの技術開発ロードマップを解説する。

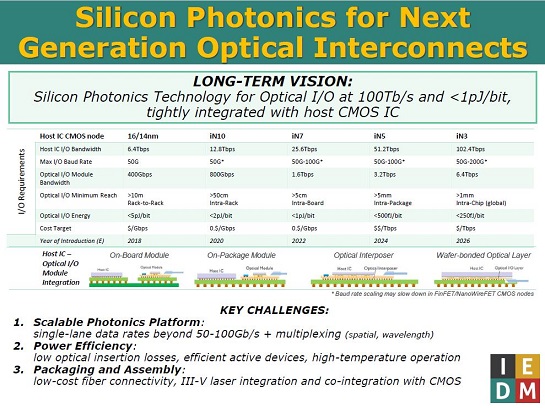

シリコンフォトニクスの技術ロードマップは、シリコン製造技術、すなわちCMOSロジックの技術ノードと密接に関連する。CMOSロジックの技術ノードが進化するとともに、シリコンフォトニクス技術も進化する。具体的には、光送受信の帯域幅が広がり、光伝送ビット当たりの消費電力が低下し、伝送速度当たりのコストが低下する。また、伝送距離の短い応用分野にも、光伝送が入り込んでいく。

将来を展望したときの大きな課題は、CMOSロジックの入出力速度が50Gビット/秒(bps)〜100Gbpsにとどまることだろう。単チャンネル当たりの動作速度向上には、限界が見え始めている。電子回路はチャンネル数を増やしたり、多値化技術を導入したりすることによって実効的な帯域幅を高める。光回路は空間多重や波長多重などの多重化技術により、光伝送の帯域幅を向上させていくことになる。

本稿では16/14nmノードから3nmノードまでの5世代にわたる、シリコンフォトニクスの性能向上を以下に展望していこう。始めは16/14nm、10nm、7nmの3世代を概観する。続いて5nmと3nmの2世代を展望していく。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増