シリコンフォトニクスの技術開発ロードマップ:福田昭のデバイス通信(144) imecが語る最新のシリコンフォトニクス技術(4)(2/2 ページ)

16/14nmノードから7nmノードで光伝送の帯域幅は4倍に増加

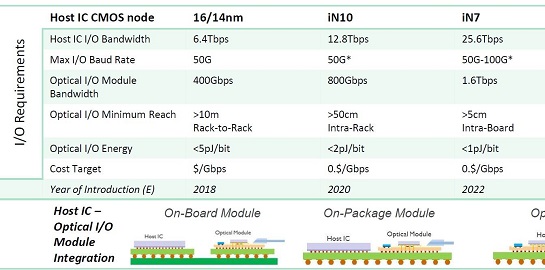

16/14nmのCMOS技術ノードは、光ファイバー伝送や光エレクトロニクスなどの世界では、現行世代である。光送受信モジュールの帯域幅は400Gbps。光伝送の最短距離は10m以上あり、データセンターではラック間の信号伝送を担う。光伝送のエネルギーは1ビット当たり5pJ以下である。伝送コストの目標値はGビット/秒当たりで数米ドルだ。

ホストとなるCMOSロジックの帯域幅は6.4Tbps、単一チャンネル当たりの伝送速度(ボーレート)は50Gボーである。

これが次世代(導入時期は2020年と推定)の10nmノードになると、光送受信モジュールの帯域幅が800Gbpsに向上する。世代ごとに帯域幅を約2倍にしていくというのが、基本的なロードマップである。光伝送の最短距離は50cmに縮まる。データセンターではラック内の信号伝送(ボード間の信号伝送)にも、光ファイバー伝送が使われるようになる。伝送コストの目標値はGビット/秒当たりで1米ドル以下とかなり厳しい。

次々世代(導入時期は2022年と推定)の7nmノードでは、光送受信モジュールの帯域幅は1.6Tbpsとさらに2倍に増える。光伝送の最短距離は5cmとさらに縮まる。ボード内の信号伝送(半導体パッケージ間の信号伝送)にも、光ファイバー伝送が使われ始める。光伝送のエネルギーは1ビット当たり1pJ以下で、16/14nmノードの5分の1に下がる。

ホストとなるCMOSロジックの帯域幅は25.6Tbpsに高まる。しかし7nmノードにおける単一チャンネル当たりの伝送速度(ボーレート)は50Gボー〜100Gボーであり、16/14nmノードとあまり変わらない。CMOSロジックのトランジスタ技術がFinFETに変わったことで、微細化によるトランジスタの動作速度の向上がそれほど見込めなくなる。これがボーレートが上がらない理由だ。

伝送帯域向上の極限を目指す5nmノードと3nmノード

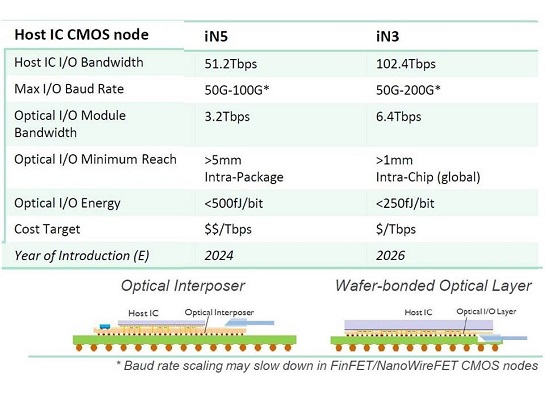

さらに先の技術ノードも見ていこう。5nmノード(導入時期は2024年と推定)になると、光送受信モジュールの帯域幅は3.2Tbpsに高まる。光伝送の最短距離は5mmとなり、パッケージ内の信号伝送(半導体ダイ間の信号伝送)にも光伝送が混じってくる。光伝送のエネルギーは1ビット当たり0.5pJ(500fJ)以下、伝送コストの目標値はTビット/秒当たりで数十米ドルとなる。

そして3nmノード(導入時期は2026年と推定)では、光送受信モジュールの帯域幅は6.4Tbpsに達する。光伝送の最短距離は1mmとなり、ついに半導体ダイ内部の信号伝送(グローバル配線)にも光伝送が使われ始める。光伝送のエネルギーは1ビット当たり0.25pJ(250fJ)以下、伝送コストの目標値はTビット/秒当たりで数米ドルにまで下がる。

以上はかなりアグレッシブなロードマップであり、技術的な障壁は低くない。既に述べたトランジスタの動作速度のほかに、電力伝送の効率(光伝送による電力損失)や高温動作、低コストの光ファイバー接続、半導体レーザーの集積化などが課題となるだろう。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

光ファイバー通信の基礎知識

光ファイバー通信の基礎知識

今回から、「IEDM 2017」で開催されたチュートリアルから、シリコンフォトニクス技術を紹介する。まずは、光ファイバー通信の基礎から始めていこう。 シリコンフォトニクスとは何か

シリコンフォトニクスとは何か

今回は、「シリコンフォトニクス」技術を紹介する。そもそも「シリコンフォトニクス」とは何か、そしてその利点と課題について解説したい。 2018年の世界8大技術トレンド、IHSが予測

2018年の世界8大技術トレンド、IHSが予測

IoT(モノのインターネット)、クラウド、人工知能(AI)――。産業界を一変させる可能性が高い技術とは何か。IHS Markitが2018年の世界8大テクノロジートレンドを予測した。 ムーアの法則、半導体業界はどう捉えるべきか(前編)

ムーアの法則、半導体業界はどう捉えるべきか(前編)

台湾Etron TechnologyのCEOであるNicky Lu氏は、「ムーアの法則」は、技術開発の方針としての役目を既に終え、ビジネス的な意味合いの方が強くなっていると述べる。半導体メーカーが今、ムーアの法則について認識すべきこととは何なのか。 ムーアの法則の終息でIDMの時代に“逆戻り”か?

ムーアの法則の終息でIDMの時代に“逆戻り”か?

米国サンフランシスコで開催されたコンピュータ関連のイベントで、半導体業界の専門家たちがパネルディスカッションを行い、「ムーアの法則」を中心に業界の今後について議論した。専門家の1人は、Appleの動きや、近年の大規模なM&Aの動きから、半導体業界はIDM(垂直統合型)に近い形に“逆戻り”するのだろうか、との疑問を投げかけた。 米半導体業界、ポスト・ムーアの技術を模索

米半導体業界、ポスト・ムーアの技術を模索

米国防高等研究計画局(DARPA)は、来たる「ムーアの法則」の終息に備え、“ポスト・ムーア時代”の技術の模索を本格化させている。材料、アーキテクチャ、設計の自動化の3つにターゲットを絞り、まずは2億米ドルを投資してプロジェクトを行う予定だ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増