多層配線工程に記憶素子を埋め込む不揮発性メモリ技術(後編):福田昭のストレージ通信(100) STが語る車載用埋め込み不揮発性メモリ(13)(1/2 ページ)

後編では、多層配線工程の中に記憶素子を作り込むタイプの埋め込み不揮発性メモリについて、その利点と、メモリセルの記憶素子を実現する技術を解説する。

ロジックとの互換性、高速・低消費、1ビット書き換えで有利

国際会議「IEDM」の「ショートコース(Short Course)」から、車載用の埋め込み不揮発性メモリに関する講座「Embedded Non Volatile Memories for Automotive Applications」の概要をご紹介している。講演者は半導体ベンダーSTMicroelectronics(STマイクロエレクトロニクス)のAlfonso Maurelli氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前回は、多層配線工程の中に記憶素子を作り込むタイプの埋め込み不揮発性メモリ技術(Embedded Emerging Memory)の概要と利点を紹介した。今回は、メモリセル技術の具体的な姿を解説していく。

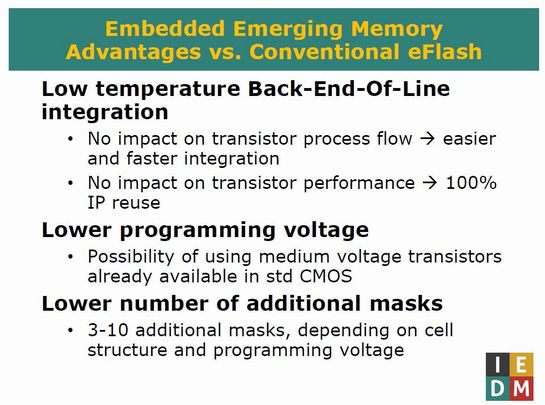

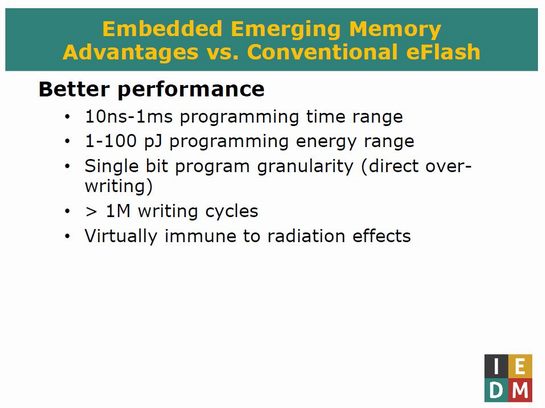

前編でも述べたように、多層配線工程の中に記憶素子を作り込むタイプの埋め込み不揮発性メモリ技術(Embedded Emerging Memory)は、埋め込みフラッシュメモリ技術と比べるといくつかの利点が存在する。まず、ロジック用トランジスタの製造工程に影響を与えないので、ロジックとメモリの混載が容易である。次に、トランジスタの性能にも影響を与えないので、マクロ(IP)を再利用しやすい。また書き込み電圧がフラッシュメモリよりも低いので、メモリセル用トランジスタの製造工程がロジック用トランジスタとあまり変わらない。さらに記憶素子の製造用マスクの追加が3枚〜10枚と少ない。そしてメモリの書き込み時間が短く、書き込みエネルギーが低く、消去作業が不要であり、1ビット単位で書き換えが可能である。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」