ポスト京は高密度がカギ、富士通が試作チップを公開:1チップに48計算コアを集積(1/2 ページ)

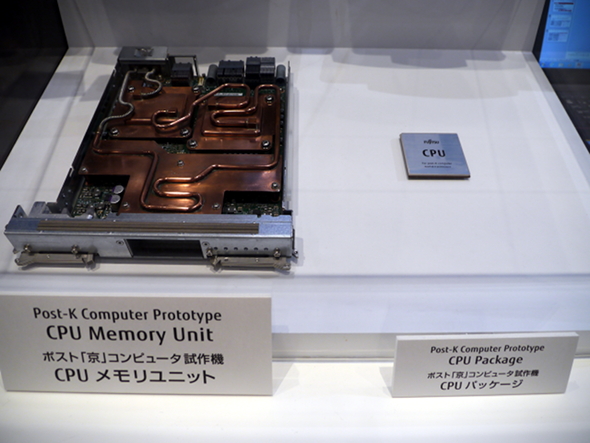

富士通は、同社のプライベートイベント「富士通フォーラム2018 東京」(2018年5月17〜18日、東京国際フォーラム)で、ポスト「京」スーパーコンピュータ(スパコン)に搭載される予定の「CPUパッケージ」とCPUパッケージを搭載した「CPUメモリユニット」の試作機を公開した。

富士通は、同社のプライベートイベント「富士通フォーラム2018 東京」(2018年5月17〜18日、東京国際フォーラム)で、ポスト「京」スーパーコンピュータ(スパコン)に搭載される予定の「CPUパッケージ」とCPUパッケージを搭載した「CPUメモリユニット」の試作機を公開した。

ポスト京は、2021年〜2022年の運用開始を目標に開発が進むスパコン。2012年より理化学研究所で現在運用されているスパコン「京」の後継機とされており、世界最高水準の汎用性と、京の最大100倍となるアプリケーション実行性能を達成しつつも、消費電力を京の約3倍となる30〜40MW程度に収めることを目標としている。

CPUのアーキテクチャはArmv8-A+SVE、1パッケージに48コアを集積

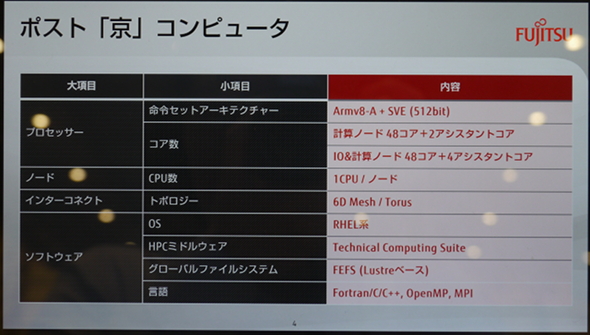

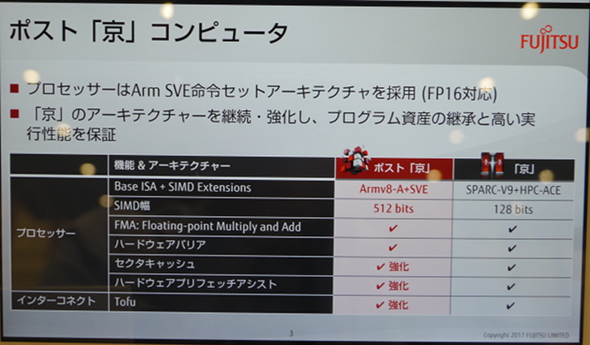

ポスト京では、ベースとなる命令セットアーキテクチャにFP16(16ビット浮動小数点)対応のArmv8-A、SIMD拡張命令セットにArmと富士通が共同開発したSVE(Scalable Vector Extensions)を採用する。SVEは128〜2048ビットのベクトル長をサポートしており、CPUがサポートする長さで動的にベクトル長を決定することが特長となる。ポスト京のCPUでは、SIMD幅が512ビットのベクトルレジスタを搭載する。京では、ベース命令セットにSPARC-V9、SIMD拡張命令セットにSIMD幅128ビット長のHPC-ACEが採用されていた。

また、指数関数補助命令とパックド単精度演算に対応し、京のCPUと比較してセクターキャッシュやハードウェアプリフェッチのアシストを強化した。京のインターコネクトとして開発された6次元メッシュトーラス構成の「Tofu」も改良が加えられ、ポスト京のインターコネクトとして引き続き採用される。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増