エッジでAIの学習も、アナログ素子で脳型回路を開発:ReRAMを応用して高電力効率に

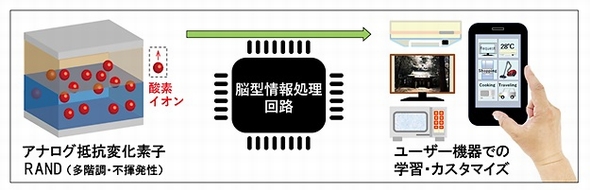

新エネルギー・産業技術総合開発機構(NEDO)らは、アナログ抵抗変化素子(RAND)を用いた、AI(人工知能)半導体向け脳型情報処理回路を開発した。エッジ側で学習と推論処理が可能となる。

新エネルギー・産業技術総合開発機構(NEDO)は2018年6月、産業技術総合研究所(産総研)、パナソニックセミコンダクターソリューションズ、北海道大学と共同で、アナログ抵抗変化素子(RAND:Resistive Analog Neuro Device)を用いた、AI(人工知能)半導体向け脳型情報処理回路を開発したと発表した。電力消費が小さく、エッジ側に推論処理と学習処理の機能を実装することが可能となる。

家電製品やロボットなどAIを実装した製品が相次ぎ登場している。ところが、AIの学習処理は演算量が膨大となるためクラウドシステム側で行い、エッジ側ではその処理結果を基に、推論処理のみを実行しているのが現状だ。

アナログ抵抗変化素子を採用、低消費電力動作を実現

今回の研究では、学習処理もエッジ側で実行できるAI半導体の開発を目指した。これによって、処理能力や消費電力の点で限界のあった端末機器やIoT(モノのインターネット)機器などでも、開発したICを搭載すればクラウド側に頼ることなく、エッジ側のみで容易にAI技術を活用することが可能となる。

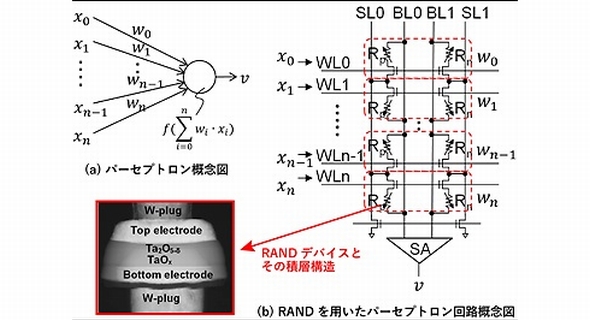

研究グループは今回、RANDを用いてデータ保存機能と積和演算機能を一体化したAI半導体向け脳型情報処理回路を開発した。RANDは、既に実用化されている不揮発性抵抗変化メモリ(ReRAM:Resistive Random Access Memory)をベースとした積層構造の素子で、パナソニックセミコンダクターソリューションズのReRAM製造プロセスを応用して開発した。

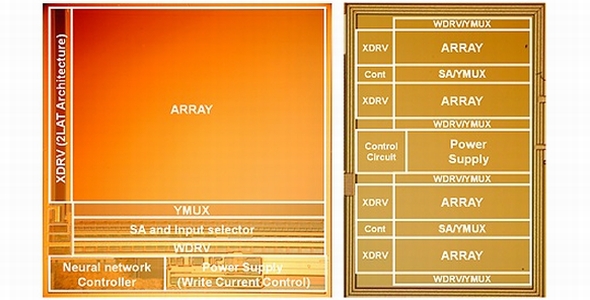

研究グループによると、180nmプロセスで開発したRANDは、30μAのダイナミックレンジで、ほぼ全てのデータが±2μAの範囲内に設定できることが分かった。この結果、RANDによる脳型情報処理回路の文字認識率は90%を超えた。さらに、線幅40nmプロセスで試作したRANDテストチップは、セル電流を抑えることに成功した。演算性能は1Wあたり66.5TOPS(Tera Operations per Second)と、極めて小さい消費電力で動作が可能だという。

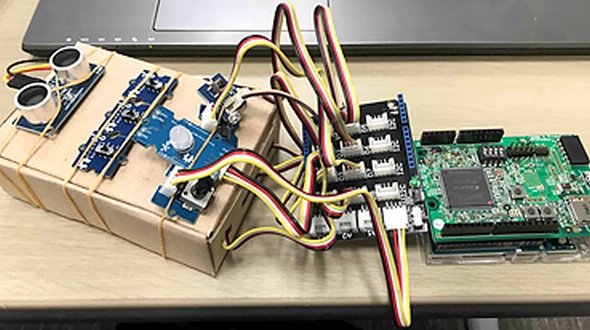

研究グループは今後、開発した技術の活用と普及に向けた環境を整備する。例えば、「誰でもAIの体験と実験が行える脳型情報処理活用プラットフォームの本格運用」や、「アナログ抵抗変化素子の作成を含む、関連技術の習得を目指した人材育成スクールの開校」などを予定している。2018年8月より実施する予定である

具体的には、AIに特化したメモリアーキテクチャを備えた「FPGA AIシールド」と、ArduinoマイコンをSPIで接続した「ソフト・ハード協調システム」を用いて、ハードウェアAIの体験ができる。なお、FPGA AIコアのHDLおよび、Arduinoサンプルライブラリーはオープンソースとして活用することが可能だ。

研究グループは、エッジ処理用途を想定した脳型AI半導体の実用化研究や微細化の追求、制御性や信頼性の向上などに引き続き取り組む。さらに、さまざまな深層学習手法に対応できるFNA(Flexible Network Architecture)としての開発も行う予定である。

関連記事

NEDO、AIエッジ・次世代コンピューティング事業を開始

NEDO、AIエッジ・次世代コンピューティング事業を開始

新エネルギー・産業技術総合開発機構(NEDO)は2018年4月20日、「AIチップ・次世代コンピューティングに関する研究開発事業」を新たに開始すると発表した。同事業により、AIエッジチップや次世代コンピューティング分野で国内の研究開発を促進し、日本の情報産業再興を目指すという。 検出精度80%以上、コンクリートひび割れ点検AI

検出精度80%以上、コンクリートひび割れ点検AI

実用に足る性能を発揮するコンクリートひび割れ点検AI(人工知能)システムが誕生した。同システムは教師あり学習とディープラーニングを併用しており、表面に汚れや傷がある状態でもコンクリートのひび割れを80%以上の精度で検出できる。システムが完成した暁には、ひび割れ点検にかかる時間が従来の10分の1となる見込みだ。 産総研ら、STOを用いた人工ニューロンを開発

産総研ら、STOを用いた人工ニューロンを開発

産業技術総合研究所(産総研)の常木澄人研究員らによる研究グループは、スピントルク発振素子(STO)を用いた人工ニューロンを開発した。これを用いたニューロモロフィック回路音声認識システムの音声認識正答率は99.6%と高い。 深層学習は専門家が足りない、米新興企業が指摘

深層学習は専門家が足りない、米新興企業が指摘

自動運転車向け深層学習ソフトウェアの開発を手掛ける米DeepScaleは、「深層学習の分野は専門家が足りていない」と指摘する。 深層学習による感情推定技術、OKIが研究開始

深層学習による感情推定技術、OKIが研究開始

OKIは、深層学習(ディープラーニング)を用いた「感情推定」技術の研究開発を始めた。2020年度の実用化を目指す。 単眼カメラで物体検出と測距、独自の深層学習で実現

単眼カメラで物体検出と測距、独自の深層学習で実現

日立超LSIシステムズは、独自のディープラーニング技術を用いて、単眼カメラの映像からリアルタイムに物体を検出し、物体までの距離推定も可能とする画像認識ソリューションの提供を始めた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

開発した研究成果のイメージ 出典:NEDO

開発した研究成果のイメージ 出典:NEDO アナログ抵抗変化素子を用いたパーセプトロン回路 出典:NEDO

アナログ抵抗変化素子を用いたパーセプトロン回路 出典:NEDO アナログ抵抗変化素子を用いたAI半導体向けの脳型情報処理回路、左が180nmプロセスで製造したチップ、右は40nmプロセスで製造した消費電力評価用テストチップの写真 出典:NEDO

アナログ抵抗変化素子を用いたAI半導体向けの脳型情報処理回路、左が180nmプロセスで製造したチップ、右は40nmプロセスで製造した消費電力評価用テストチップの写真 出典:NEDO ソフト・ハード協調システムの一例 出典:NEDO

ソフト・ハード協調システムの一例 出典:NEDO