2xnm技術で試作した40Mビット埋め込みMRAM(後編):福田昭のストレージ通信(110) GFが語る埋め込みメモリと埋め込みMRAM(10)(1/2 ページ)

2xnm世代のCMOSロジック製造技術によって記憶容量が40Mビット(5Mバイト)の埋め込みMRAMマクロを試作した結果を報告する後編である。ここでは、長期信頼性(書き換えサイクル数とデータ保持期間)とはんだ付け耐熱性に関する試験結果を紹介する。

125℃の高温下で100万回の書き換えサイクルに耐える

今回は前後編の後編である。前編を覚えておられない方や未読の方は、一度、前編を読まれてから、本編をお読みすることを強くおすすめする。

後編では、2xnm世代のCMOSロジック製造技術によって40Mビット(5Mバイト)の埋め込みMRAMマクロを試作した結果から、長期信頼性(書き換えサイクル数とデータ保持期間)とはんだ付け耐熱性に関する試験結果をご紹介する。

前編で述べたように、試作した埋め込みMRAMのMTJ(磁気トンネル接合)には、SRAM代替用MTJ「スタックA(Stack-A)」と、フラッシュメモリ代替用MTJ「スタックB(Stack-B)」がある。

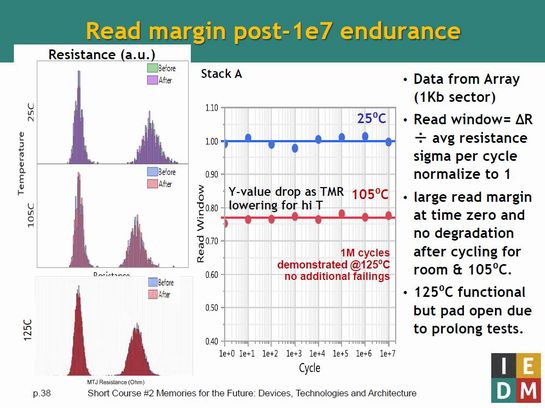

書き換えサイクル数は、SRAM代替用MTJ「スタックA(Stack-A)」のセルアレイ(1Kビット)で測定した。温度条件は25℃、105℃、125℃と変化させている。25℃と105℃の温度条件では、100万回の書き換えサイクルを経た後に十分な読み出しマージンを確保できた。ただし温度が上昇すると、読み出しマージン(トンネル磁気抵抗比)そのものは低下している。また125℃の温度条件では、100万回の書き換えサイクルを経ても不良は増加しなかった。

温度条件を変化させたときの書き換えサイクル特性(スタックA)。左は書き換えサイクル試験を完了した後に、読み出し動作におけるMTJの抵抗値のばらつきを異なる温度条件で調べた結果。中央は書き換えサイクル数と読み出しマージンの関係。書き換えサイクル数が増加しても、読み出しマージンは初期値とほとんど変わっておらず、100万回の書き換えサイクルを経ても劣化はみられない。出典:GLOBALFOUNDRIES

温度条件を変化させたときの書き換えサイクル特性(スタックA)。左は書き換えサイクル試験を完了した後に、読み出し動作におけるMTJの抵抗値のばらつきを異なる温度条件で調べた結果。中央は書き換えサイクル数と読み出しマージンの関係。書き換えサイクル数が増加しても、読み出しマージンは初期値とほとんど変わっておらず、100万回の書き換えサイクルを経ても劣化はみられない。出典:GLOBALFOUNDRIES125℃の高温条件で、10年間のデータ保存期間を確保

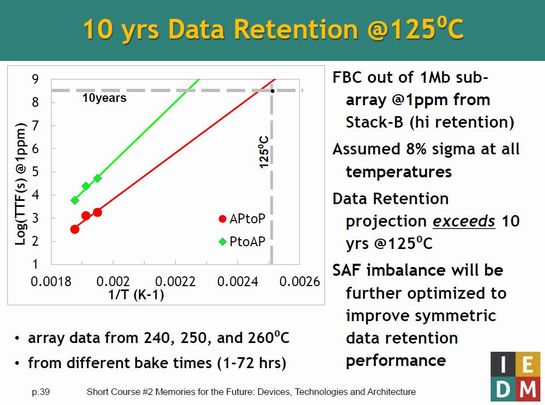

次はデータ保持期間である。こちらはフラッシュメモリ代替用MTJ「スタックB(Stack-B)」のセルアレイで測定した。設計目標は、1Mビットのセルアレイに対して温度が125℃の条件で、10年間のデータ保存期間をへたときに「1ppm以下の不良率」である。

240℃〜260℃の高温条件下による加速試験の結果、磁気トンネル接合(MTJ)が平行(P)から反平行(AP)に移行した場合と、反平行(AP)から平行(P)に移行した場合の両方とも、設計仕様を満足することができた。

ただしデータが反平行(AP)状態で保存された場合と、平行(P)状態で保存された場合では、データ保持特性に違いが生じた。この非対称性を緩和することが、今度の課題として残ることとなった。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円